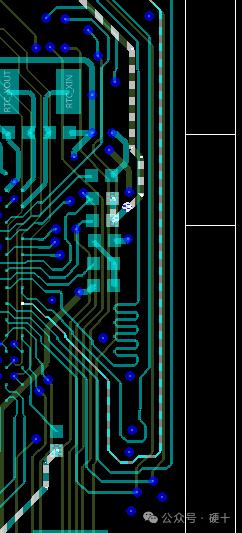

注意 PCB走線間距,比“串擾”危害更大的是“阻抗變化”

在PCB設計中,工程師們往往對高速信號的完整性保持高度警惕,卻容易忽視低速信號走線的阻抗控制問題。當相鄰走線間距呈現不規則變化時,即便信號速率不高,仍然會引發意想不到的信號質量問題。這種間距變化帶來的阻抗擾動,遠比單純考慮串擾問題更值得關注。

本文引用地址:http://www.j9360.com/article/202503/468190.htm一些速率雖然不算特別高,但是對時序、信號質量有要求的數字接口,例如“SDIO”。我要注意走線間距的問題。

如果走線可以間距足夠的大,例如滿足3W,并且可以用GND隔離,并且足夠的空間打GND地孔,那么也沒什么糾結的。但是往往我們沒有那么多足夠的空間來走線。這時候,我們需要判斷讓兩根線的間距增大一些。但是不要盲目鋪GND

為什么不要隨便在高速線旁邊鋪銅?

那么,我們就像知道,此時50Mbps的信號,或者100Mbps的信號走線是否會干擾相鄰信號。

我們實際場景中,只能做到2W,是否有串擾問題呢?

空間受限時的妥協方案

若PCB空間不足,可采取以下平衡策略:

優先級分級 :

CLK信號 :必須滿足4W間距或地線隔離。

CMD信號 :次優先級,≥3W間距。

DAT0-DAT3 :組內等長優先,組間允許局部放寬至2.5W(需SI驗證)。

局部密度調整 :

非關鍵信號(如CD檢測)可縮小間距至2W。

犧牲布線層 :

將SDIO信號單獨布置在一層,避免與其他高速信號(如DDR、USB)平行。

串擾增加

間距從 3W 減至 2W 時,相鄰信號線間的電場耦合增強,串擾噪聲可能增加 30%~50%(差分對更敏感)。

高頻信號(如 PCIe Gen4 以上)的近端串擾(NEXT)可能超出規范要求,導致誤碼率上升。

阻抗偏差

差分對間距縮小會降低差分阻抗(典型值下降約 5~10Ω),若設計容差為 ±10%,可能超出允許范圍。

單端線與參考平面的間距變化也會影響單端阻抗,導致反射增加。

EMI 輻射增大

緊密間距會增加共模電流輻射,尤其是當差分對不平衡時,EMI 可能超出 FCC/CE 認證限值。

比“串擾”危害更大的是“阻抗變化”

如果我們做不到3W,把間距縮小為2W,除了串擾問題,還有什么問題呢?

當 PCB 走線間距無法滿足 3W 規則(即線中心距為 3 倍線寬),而只能采用 2W 時,會對信號完整性和 EMI 產生顯著影響,具體問題及對策如下:

雖然100MHz以下的信號對2W間距的相鄰走線串擾影響是有限的,但是會影響阻抗,間距的變化會導致阻抗變化,從而引起反射,導致信號質量變差。我們還是把2W優化為2.5W。

評論