SiC JFET并聯難題大揭秘,這些挑戰讓工程師 “頭禿”!

隨著Al工作負載日趨復雜和高耗能,能提供高能效并能夠處理高壓的可靠SiC JFET將越來越重要。我們將詳細介紹安森美(onsemi)SiC cascode JFET,內容包括Cascode(共源共柵)關鍵參數和并聯振蕩的分析,以及設計指南。本文為第一篇,聚焦Cascode產品介紹、Cascode背景知識和并聯設計。

本文引用地址:http://www.j9360.com/article/202503/467642.htm簡介

大電流操作通常需要直接并聯功率半導體器件。出于成本或布局的考慮,并聯分立器件通常是優選方案。另一種替代方案是使用功率模塊,但這些模塊實際上也是通過并聯芯片實現的。本文總結了適用于所有并聯電壓柵控型功率半導體(如SiC JFET cascode、SiC MOSFET、Si MOSFET、IGBT等)的通用最佳實踐方案。并聯Cascode等高增益器件尤其具有挑戰性。遵循這些實踐方案有助于成功實現 SiC JFET cascode的并聯工作。

Cascode背景知識

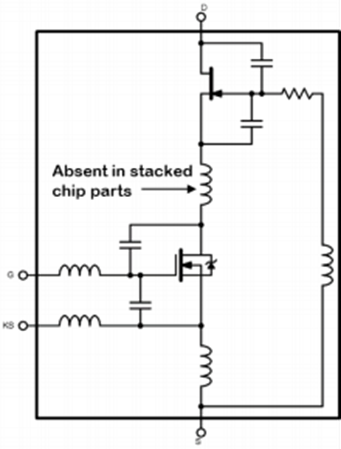

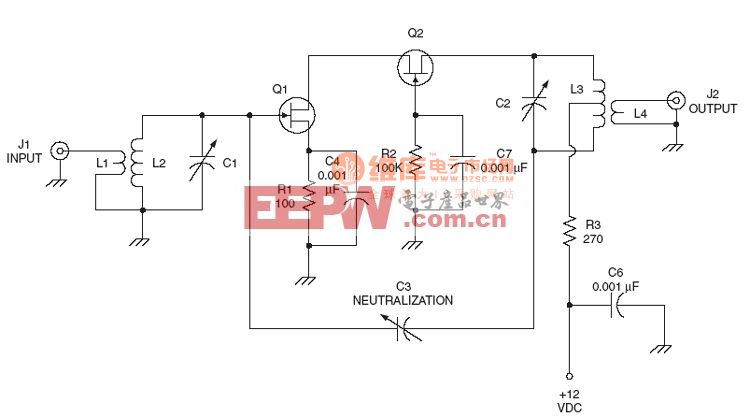

如圖 1 所示,cascode 結構是由一個常開 SiC JFET(碳化硅結型場效應晶體管) 與一個低壓 Si MOSFET (硅金屬-氧化物半導體場效應晶體管)串聯而成。JFET的 柵極直接連接到 MOSFET 的源極,JFET 的柵極電阻是 JFET 芯片的一部分。

MOSFET 漏極-源極電壓是 JFET 柵極-源極電壓的反相,從而使cascode 結構呈現常關特性。正如《Cascode入門》中所述,Cascode與其他功率晶體管的主要區別在于,一旦 VDS超過 JFET 的閾值電壓,就沒有柵極-漏極電容。 這是因為 JFET 沒有漏極-源極電容,因此Cascode結構的開關速度極快。 這一特性與寄生電感問題相結合,是Cascode并聯工作中需要解決的核心問題。

圖 1 帶雜散阻抗的Cascode結構

并聯的挑戰

■ 靜態電流失配

靜態電流失配是指并聯器件在開關瞬態穩定后,并聯器件之間的電流不匹配現象。對于具有熱不穩定性(如負溫度系數導通電阻的舊式硅二極管或穿通型IGBT)的器件尤其值得關注。如果各個器件導通電阻的變化(分布)足夠小(即經過分選的器件),并且為了彌補不可避免的電流失配而留有裕量,則具有負溫度系數的器件可以成功并聯。

有一個廣為流傳的誤解,認為正溫度系數導通電阻能強制均流,從而有利于并聯。實際上,正溫度系數僅確保熱穩定性。現代功率半導體(包括 SiC JFET、SiC MOSFET、場截止 IGBT 等)的參數分布較窄,這進一步強化了人們對于正溫度系數在均流方面具有強大作用的看法,但決定靜態均流的是參數分布和共同的散熱裝置。

■ 動態電流失配

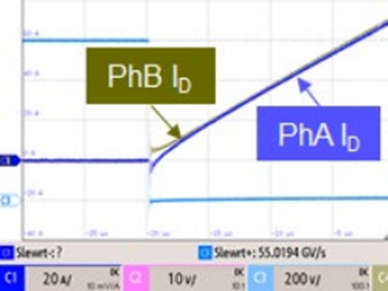

圖2 閾值電壓失配導致的動態電流失配

動態電流失配是由MOS柵控器件和JFET器件固有的器件間閾值電壓變化、電流環路的不對稱性以及柵極驅動器之間傳播時延差異(如果適用的話)所引起的。閾值電壓較低的部件會較早導通、較晚關斷,因此會產生更多的硬開關損耗。在開關頻率非常高的情況下,這種情況更加令人擔憂。

圖2顯示了兩個并聯cascode電路在導通時的動態失配。電流失配迅速減小是典型的現象,因為穩態均流主要由RDS(on)決定。在計算中,使用數據表中RDS(on)和RθJC的最大值,可以為并聯時的靜態和動態電流失配提供安全裕量。

并聯設計還有哪些挑戰?后續推文我們將繼續介紹。

第二篇跳轉:SiC JFET并聯的五大難題,破解方法終于來了!(http://www.j9360.com/article/202503/467644.htm)

第三篇跳轉:速看!SiC JFET并聯設計白皮書完整版(http://www.j9360.com/article/202503/467646.htm)

評論