?AMD Zen5、Zen6架構細節曝光

AMD 將在明年推出 Zen5 架構的銳龍 8000 系列、霄龍 9005/8005 系列,更下一代的 Zen6 架構也已經嶄露頭角,據說可以支持到史無前例的 16 通道內存。

本文引用地址:http://www.j9360.com/article/202310/451160.htm現在,MLID 曝光了一份 AMD 架構路線圖,列出了 Zen5、Zen6 的不少細節,尤其是前者料很猛。

AMD Zen 架構家族采取了波動式升級策略,一代大改、一代小改交替進行,比如 Zen5 就會是一次大改,Zen6 則是一次小改。

Zen5 架構代號 Nirvana(涅盤),預計會將 IPC 提升大約 10-15%,對比 Zen3 19%、Zen4 14%似乎不是很突出,但一則這是早期預估目標,不排除未來進一步提升,二則也要考慮頻率同步提升所帶來的性能增益。

另一點就是首次大范圍應用「大小核」混合架構,搭檔 Zen5c,但應該主要面向筆記本。

制程工藝方面,CCD 升級為 3nm,IOD 升級為 4nm。

尤為值得注意的是,Zen5 將會首次支持原生 16 核心的 CCD,相比這幾代的 8 核心翻了一番,使得桌面主流 32 核心成為可能。

其它方面,一級數據緩存容量從 32KB 增至 48KB,同時 8 路關聯升級為 12 路,不過一級指令緩存仍是 32KB, 二級緩存仍是每核心 1MB。

分支預測繼續提升性能和精度,數據預取繼續改進,ISA 指令與安全繼續增強,吞吐能力也進一步擴大,包括 8 寬度的分派與重命名、6 個 ALU 算術邏輯單元、4 個載入與 2 個存儲,等等。

Zen6 架構代號 Morpheus(希臘神話夢神摩耳甫斯),制造工藝將會進一步升級到 CCD 2nm、IOD 3nm,而且 CCD 再次升級為原生 32 核心!

IPC 性能預計再提升 10%,同時加入面向人工智能、機器學習的 FP16 指令,以及新的內存增強。

此外,Zen6 據說還會有新的封裝技術,可能會將 CCD 堆疊在 IOD 之上,可以達到縮小芯片面積、提升內部通信效率,但就沒法直接堆成 64 核心了。

Zen6 大概率會繼續沿用 AM5 封裝接口,畢竟 AMD 承諾過要支持到 2026 年。

Zen5:Zen 架構誕生以來最大飛躍

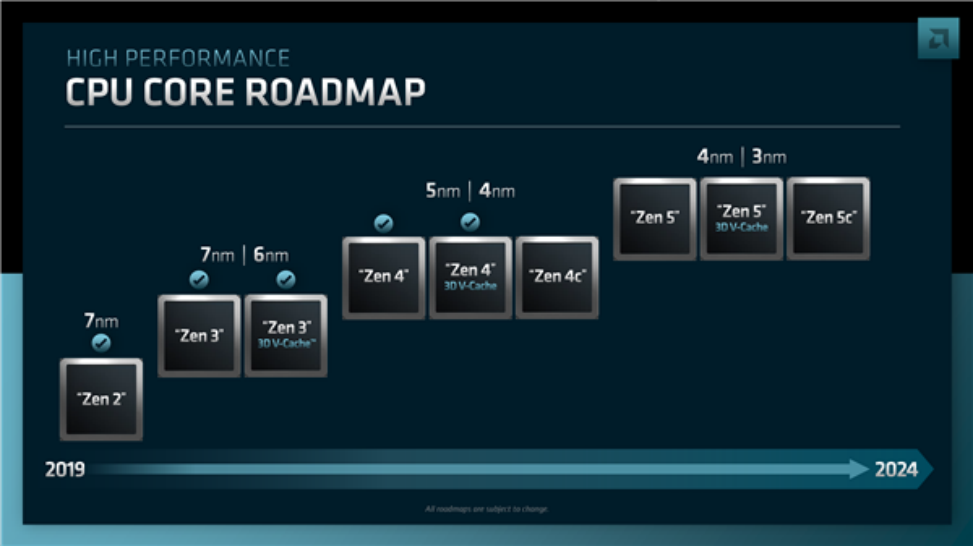

AMD 早已在官方路線圖上大大豐富地列出了下一代 Zen5 CPU 架構,升級為 4nm、3nm 工藝,2024-2025 年陸續推出。

其中,服務器產品代號 Turin,桌面上是 Granite Ridge,筆記本上有 Strix Halo、Fire Range,不少規格都已經曝光,相當震撼。

RedGamingTech 現在首次曝光了 Zen5 的性能跑分,來自 AM5 桌面款的銳龍 8000,早期工程樣品,頻率、功耗等測試條件未知。

最多還是 16 個核心,CineBench R23 多核心跑分大約 49000,相比目前的 38000 分左右提高了幾乎 30%!

同時,12 核心 36000 分左右,8 核心 23000 分左右,6 核心 17000 分左右,與核心數量幾乎呈完美的線性關系,都有顯著提升。

單核心跑分在 2500-3000 分左右,依然超過了如今 6GHz 高頻率的 i9-13900KS!

別忘了,這還只是工程樣品,后期仍有很大的提升空間,16 核心的多核跑分突破 5 萬分應該不是啥事兒。

值得一提的是,被譽為 Zen 架構之父的 Jim Keller 早期曾經曝光過一張幻燈片 (后被刪除),顯示 Zen5 SPECint 跑分一枝獨秀,遙遙領先,沒有任何對手。

Jim Keller 雖然早已離開 AMD,但是他參與了 Zen 架構的設計,可以說為 AMD 這么多年的發展奠定了堅實的基礎。

之前就有說法稱,Zen5 將是一次大改款,也是 Zen 誕生以來提升幅度最大的一次,甚至超越 Zen2 到 Zen3 的變化。

同時,Zen5 時代 AMD 也將正式全面采用大小核心設計,Zen5 搭配衍生版本 Zen5c,但后者的 IPC、ISA 都不變,主要只是精簡緩存,這和 Intel 的異構大小核截然不同。

Zen6 霄龍首曝:史上第一次 16 通道內存

根據官方路線圖,AMD 將在明年推出 Zen5 架構家族,其中在 EPYC 霄龍服務器端將延續現有體系,劃分為 Zen5(代號 Turin)、Zen5 3D V-Cache、Zen5c 三個版本,制造工藝升級為 3/2m(應該分別是 CCD、IOD)。

那么再往后的 Zen6 呢?

最新曝光的一張路線圖顯示,AMD Zen6 架構霄龍的代號為「Venice」,也就是意大利水城威尼斯,延續該系列一貫以意大利城市作為代號的傳統。

封裝接口改為 SP7,而現在的 Zen4 家族是 SP5,這意味著下一代 Zen5 家族會使用 SP6,一代換一次。

規格方面只顯示了一點,內存通道有 16 個、12 個兩種,這將是歷史上第一次做到 16 通道,而現在最高只有 12 通道。

據說,Zen6 架構霄龍 CCD 部分的制造工藝將升級為 2nm,IOD 則可能是 3nm。

順便回顧一下 AMD 歷代 CPU 架構的內部代號和對應工藝:

Zen 2 (7nm) – Valhalla(英靈殿)

Zen 3 (7nm) – Cerberus(刻耳柏洛斯,古希臘神話中的地獄三頭犬)

Zen 4 (4/5nm) – Persephone(珀耳塞福涅,古希臘神話冥后)

Zen 5 (3/4nm) – Nirvana(涅盤)

Zen 6 (2/3nm) - Morpehus(摩耳甫斯,古希臘神話夢神)

另外,路線圖上可以看到 AMD 下一代 Instinct MI400 系列加速器,包括三個版本:MI400A 肯定是 CPU+GPU 融合方案,MI400X 是純 GPU 方案,MI400C 就不知道了。

Intel 這邊,至強處理器明年是純大核 Granite Rapids(GNR)、純小核 Sierra Forest(SRF),后續升級版分別是 Diamond Rapids(DMR)、Clearwater Forest(FCS),但是在 Intel 官方路線圖上,Diamond Rapids 至少目前消失了。

加速器方面是下一代 Falcon Shore,分為 X、G 兩個版本,但不清楚什么區別。

它最初規劃是 CPU+GPU 融合,但現在已經退回到純 GPU。

評論