最新超導量子位研究 成功導入CMOS制程

量子計算機可望在特定應用領域帶來巨變,包含材料合成、藥物開發、網絡安全等等。在量子電路的運算模型中,量子邏輯閘(簡稱量子閘)利用少數量子來進行基本運算,與傳統數字電路里的邏輯閘雷同。量子是量子電路的基本構件。全球正在努力開發具備不同類型量子位的量子運算平臺,期望能將應用從實驗室擴展到全球。

其中一項前景看好的量子運算技術透過超導電路運行。Anton Potocnik是深耕量子運算領域的imec資深研究員,他表示:「超導量子位的能量狀態相對容易操控,經過這幾年,研究人員已能將越來越多的量子進行耦合,進而實現更進階的量子糾纏—這是量子運算發展的其中一大支柱。除此之外,全球各地的研究團隊已經公開展示超導量子位的優異性能,包含維持量子態長達數百微秒的相干時間,以及達到一定水平的閘保真度(gate fidelity),兩者都是量子運算的重要指標。」

相干時間提供我們有關維持量子態(亦即數據保存)的時間信息;閘保真度則量化了理想的邏輯閘與其在實體量子電路對應的物理閘之間的運算誤差。

大型量子計算機的發展阻礙:變異度問題

目前為止,剛剛提到的量子運算效能只能在實驗室看到成果,利用雙角蒸鍍法(double-angle evaporation)與剝離成形(lift-off)技術來制出最關鍵的組件結構:約瑟夫森接面(Josephson junction)。

Anton Potocnik解釋:「基本上,超導量子位是非線性LC諧振電路,內含一個非線性電感(L)與一個電容(C)。約瑟夫森接面作為非線性且非散熱的電感組件,能讓我們操控量子位的能量狀態,例如代表|0>與|1>的迭加態。為了把能耗降到最低,也就是盡可能地延長相干時間,約瑟夫森接面與電容的結構內部必須避免各個接口產生瑕疵。在任一接口存在原子大小的瑕疵都有可能導致量子位損失能量。因此,雙角蒸鍍法與剝離成形是較為理想的制程方案,它們能制出接近無瑕的接口。」

盡管如此,這些制程技術有一大缺點,那就是難以實現量子位數量的規模化。蒸鍍接面在約瑟夫森效應下產生的超導電流存在一定的變異度,這就阻礙了大規模量子運算。此外,制程技術也會限制超導材料的選擇,進而阻礙量子位進一步改良。

替代方案:CMOS相容制程

imec博士研究員Jeroen Verjauw表示:「imec團隊已經探索了超導電路的替代制程方案,主力放在所謂的覆蓋式約瑟夫森接面(overlap Josephson junction),僅用與CMOS兼容的材料與技術制成,藉此發揮先進CMOS制程所具備的可靠度與再現性(reproducibility)優勢,以控制量子位變異度并實現規模化。」

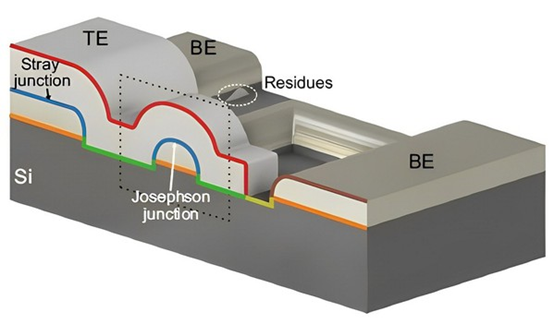

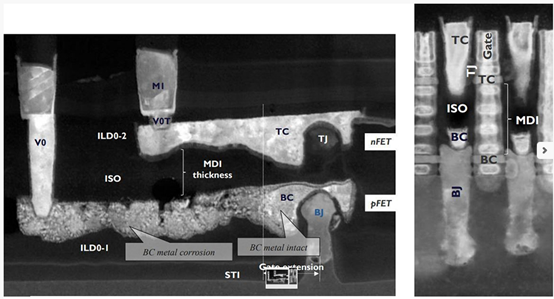

覆蓋式接面包含下層(BE)與上層(TE)兩個電極,中間以絕緣層薄膜分隔。這些電極經過兩次圖形化處理,期間導入一次真空制程,真空時會自然生成金屬氧化物,后續進行氬氣(Ar)蝕刻時必須移除。

圖一 : 覆蓋式接面的截面示意圖:上下層電極之間的重迭區域會定義出約瑟夫森接面(以及寄生雜散接面)的圖形。側壁會因為蝕刻制程而出現殘留物。綠色那層標示了經過氬氣蝕刻制程后產生的受損多晶硅層。

Jeroen Verjauw指出:「不過,氬氣蝕刻制程有一定的風險,之前就傳出會造成能量耗損。」

量子運算生力軍:CMOS制程登場

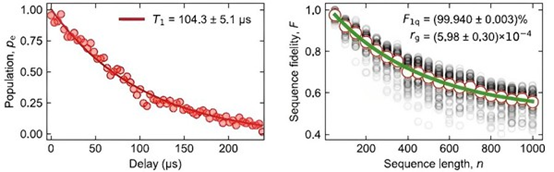

imec研究員Tsvetan Ivanov表示:「我們的實驗室展示了超導量子位的優異效能,相干時間長達數百微秒,平均閘保真度達到99.94%,與其他先進量子芯片效能相當。不同的是,這是首次透過CMOS兼容技術來獲得進展,像是濺鍍沉積與蝕刻制程。改良目前的覆蓋式接面制程就能取得這些突破性成果,具體作為包含簡化制程步驟與減少接口數量—藉此降低能耗損失的風險,還有優化氬氣蝕刻制程,并且僅用鋁(Al)來制作電極。」

圖二 : (左)量子位能量釋放的量測結果;(右)平均閘保真度(gate fidelity)與平均閘錯誤率(error per gate)。

三大發展目標:進入12吋晶圓廠、降低損耗、提升再現性

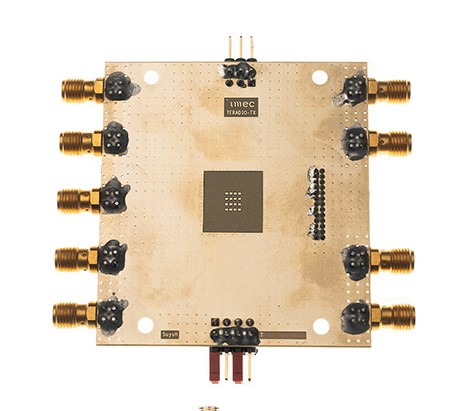

imec此次發表的研究成果目前僅在實驗室的測試基板上獲得驗證。Tsvetan Ivanov表示:「雖然如此,此次展示的制程方法仍是重要的里程碑,預告著未來超導量子電路有望進入12吋晶圓CMOS制程。我們很快就能將這些超導電路的制程技術轉移至imec的12吋晶圓廠。我們亟欲驗證上述的量子態維持時間能否在大尺寸晶圓上達到相同結果。」

Jeroen Verjauw接著說道:「為了研究能耗來源,我們還設計了測試芯片。首批研究結果顯示,能量損失主要源于組件結構的表面,而非接面的那層。這項發現令人振奮,因為只要鎖定應用導入專用的表面處理技術,就有可能改善問題。最后,我們的制造方案提供了在大尺寸晶圓上大規模制造量子位的方法,減緩量子位頻率等變異度問題。」

但在實際應用超導量子計算機之前,仍有一些問題需要解決。Anton Potocnik總結:「超導量子位(毫米等級)與像是半導體自旋量子位(奈米等級)相比,仍舊相對較大。我們正在針對組件微縮進行研究,也在努力研發算法。目前我們做出的量子位還不盡理想,所以要從理論出發,持續開發具備更能容許損耗與誤差的算法,同時發展量子錯誤更正協議。此外,我們還會需要可規模化且經過精密校正的儀器來連接持續增加的超導量子位,進而進行操控與讀取有用數據。」

結語

imec量子運算研究計劃主持人Kristiaan De Greve認為,此次的研究成果是邁向超導量子位規模化的重要里程碑,憑借業界標準制程所具備的操控與準確度優勢,將能克服關鍵挑戰。他表示:「未來很可能需要成千上百萬個量子位來構成量子運算處理器,所以突破變異性與產量的限制會是關鍵。也因此,imec投入大量資源來了解這些發展限制并訂定相關標準,同時善用我們在先進制程管制方面的經驗,引進創新的解決方案。」

imec量子運算研究計劃組長Danny Wan最后補充:「imec量子運算研究計劃的成員全都希望能將量子運算帶出實驗室,擴及全球,不論是采用超導體或半導體。此次刊載于《NPJ Quantum Information》的研究成果大大助長了信心,證實我們走在正確的道路上。」

(本文由imec提供;編譯/吳雅婷)

評論