imec展示56Gb波束成形發射機 實現高功率零中頻的D頻段傳輸

于本周舉行的國際電機電子工程師學會(IEEE)射頻集成電路國際會議(RFIC Symposium)上,比利時微電子研究中心(imec)發表了一款基于CMOS技術的先進波束成形發射機,用來滿足D頻段的無線傳輸應用。該發射器具備優異的輸出功率及能源效率,同時支持每通道56Gb/s的超高數據傳輸率。該組件也是比利時微電子研究中心(imec)研究人員目前正在開發的四路波束成形收發機芯片之核心構件。運用這項技術,他們希望可以協助部署新一代100GHz以上的高頻短距無線傳輸服務。

新一代短距無線應用以實現每秒數百億位(Gb/s)的超高傳輸率聞名,這些應用開創了機運無限的時代。不論是探索無線傳輸失效安全機制的數據中心、固定無線存取(FWA)網絡的部署或是用來打造延展實境(XR)體驗的無線熱點,這些應用全都涵蓋了100GHz~300GHz的次太赫茲(sub-THz)頻段。

這些頻段所提供的超高帶寬只是其中一項關鍵性能。由于波長更短,這些頻段還能縮小天線的尺寸,應用于構型更緊湊的存取點與手持裝置。最后,超高的感測分辨率將在電競、智慧建筑、工業5.0等未來應用帶來寶貴的價值,通訊與感測(即通感)功能將在這些應用交織并用。

imec研究計劃主持人Joris Van Driessche解釋:「但是當進入100GHz以上的高頻領域,CMOS技術遇到各種問題。第一項挑戰是達到一定的輸出功率,以克服這些高頻段具備較高路徑損失的問題。另外,寬帶電路的設計也是難上加難,不僅要具備良好的動態范圍,還要把功耗控制在合理范圍。這些挑戰都是我們采用CMOS技術來創新開發D頻段波束成形發射機的核心重點。」

高傳輸率、低功耗的D波段CMOS波束成形發射機

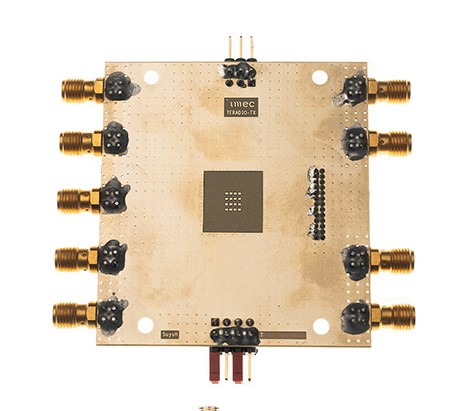

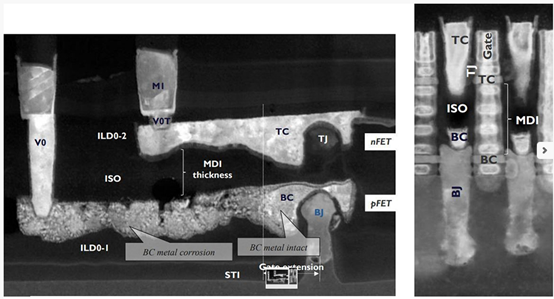

imec所研發的發射機是一款四路波束成形收發機的組件,并以120GHz~145GHz的頻率運行。該組件采用22奈米全空乏型絕緣層上硅(FD-SOI)制程,每個發射通道的占用面積僅有1.17x0.3mm2且功耗為232mW。在imec設定的操作狀態下,該組件的輸出功率在進行16QAM調變后達到3dBm,經過64QAM調變后則為2dBm,這與其他D頻段CMOS收發機相比,其發射功率的表現特別出色。

這款發射機在本地振蕩器(LO)電路設置波束成形功能,以控制具備高增益的窄波束朝向特定的方向傳輸,另結合零中頻(IF)的收發機結構,藉此減少訊號路徑上的組件數量。因此,訊號路徑的動態范圍可以避免損耗,并實現較廣的射頻頻寬。此外,imec采用的設計具備寬帶的模擬基頻,這包含了高達14GHz的通道帶寬,所以能在超大的頻率范圍內達到每信道56Gb/s的超高數據傳輸率。

imec研究計劃主持人Joris Van Driessche表示:「我們的芯片還有另一個特點,那就是完整性。與其他的競爭方案不同,我們的收發機成功在四路通道上無縫整合了用于波束成形的本地振蕩器(LO)與完整的模擬基頻,并提供完整的射頻訊號鏈和波束成形性能。據我們所知,這是重大的領先創舉。」

廣邀研發伙伴來探索技術潛能

Van Driessche總結:「我們在IEEE射頻集成電路國際會議(RFIC Symposium)上發表的論文著重于展現我們利用這款全新開發的波束成形發射機所實現的研究成果。但在這之后,imec的這項研究便開始帶頭開發一款完整的四路波束成形收發機芯片,目前正在進行進一步的特性分析。透過這款芯片,我們希望能建立一套D頻段無線系統,未來將能提供研究伙伴用來進行實驗,包含波束成形技術、通感組合(joint communication and sensing)應用等,同時證實了CMOS技術確實可用于新一代100GHz以上的高頻短距無線傳輸。」

評論