聯發科與瑞薩采用Cadence Cerebrus AI方案 優化芯片PPA

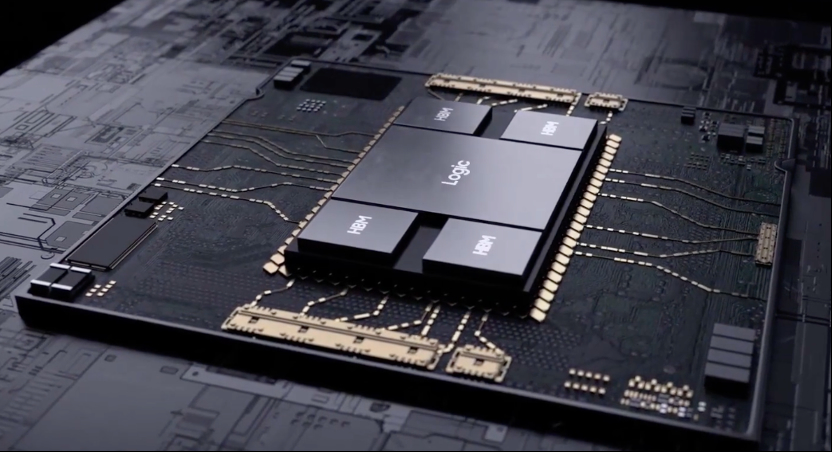

Cadence Cerebrus 運用革命性的AI技術,擁有獨特的強化學習引擎,可自動優化軟件工具和芯片設計選項,提供更好的 PPA進而大幅減少工程端的負荷和整體流片時間。例如,Cadence Cerebrus 布局優化功能,使客戶能夠超越常人的設計潛力縮小芯片尺寸。因此,Cadence Cerebrus 與完整的 Cadence 數字產品線相結合,藉由業界最先進從合成、設計實現到簽核的完整數字全流程,提供了突破性的工程設計優勢。

本文引用地址:http://www.j9360.com/article/202206/435063.htmCadence資深副總裁暨數字與簽核事業群總經理滕晉慶(Chin-Chi Teng)博士表示:「我們一直在尋找新的方法來幫助我們的客戶提高生產力,而Cadence Cerebrus以其 AI 能力減少耗時手動工作,使得工程師可以專注于更重要的項目。我們推出 Cadence Cerebrus的一年內,就顯著地看到我們的客戶快速采用并開始實現產品的全部潛力。客戶如聯發科技和瑞薩電子獲得PPA 改善和生產力提升,因而他們現在已經在量產計劃中廣泛采用了該工具。」

聯發科技硅產品開發部門資深副總經理謝有慶表示:「在聯發科技,我們致力于提供最佳的 PPA,因此以AI為基礎的Cadence Cerebrus解決方案成為我們最新先進制程項目最合理的選擇。在SoC模塊設計上,Cadence Cerebrus 布局規劃優化功能.可將該模塊芯片面積縮小 5%,并將功耗降低6% 以上。在獲得生產力提升、PPA更加優化且更易于整合到聯發科技CAD 流程等全面

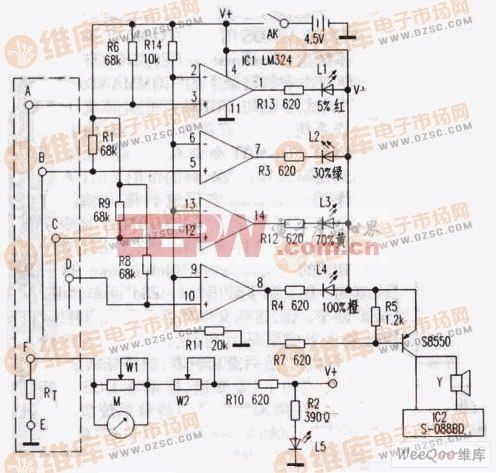

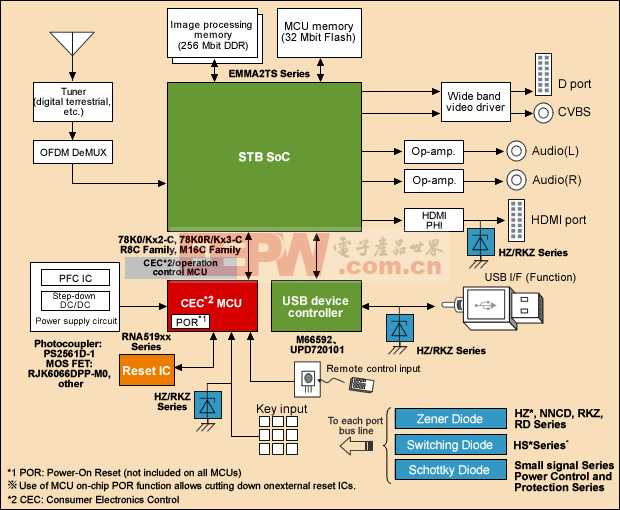

瑞薩電子公司共享研發 EDA 部門的副總裁Toshinori Inoshita 表示:「我們需要能夠改進各種節點和設計類型PPA 的自動化方法,藉由采用并優化 Cadence Cerebrus 以滿足我們所有特別的設計需求,并取得了許多顯著的設計成果。在先進制程 CPU 設計中,我們體驗到了更好的性能,在總體負時序裕量 (TNS) 提高了 75%。此外,我們采用Cadence Cerebrus 大幅降低了關鍵 MCU 設計的泄漏功率,讓我們進一步提高性能和生產力,并縮短流片時間。

評論