3D DRAM技術是DRAM的的未來嗎?

5月25日,有消息傳出,華為將在VLSI Symposium 2022期間發表其與中科院微電子研究所合作開發的 3D DRAM 技術。隨著“摩爾定律”走向極限,DRAM芯片工藝提升將愈發困難。3D DRAM就成了各大存儲廠商突破DRAM工藝極限的新方案。

本文引用地址:http://www.j9360.com/article/202205/434610.htmDRAM工藝的極限

目前,DRAM芯片最先進的工藝是10nm。據公開資料顯示,三星早已在2020年完成了10nm制程DRAM的出貨;美光和SK海力士也在2021年完成了10nm DRAM產品的量產。

那么,10nm是DRAM工藝的極限嗎?

在回答這個問題之前,我們先來看看DRAM工藝的發展歷程。如圖1所示,DRAM的工藝不是直接從20nm一下到10nm。而是在20nm之后,又細分成了1Xnm(16nm-19nm)、1Ynm(14nm-16nm)、1Znm(12nm-14nm)、1anm(10-12nm)。可以看出,在20nm之后,DRAM工藝的提升的確越來越難,縮小2nm,就意味著前進了一大步。

圖1 內存廠商路線圖(來源:前瞻研究院)

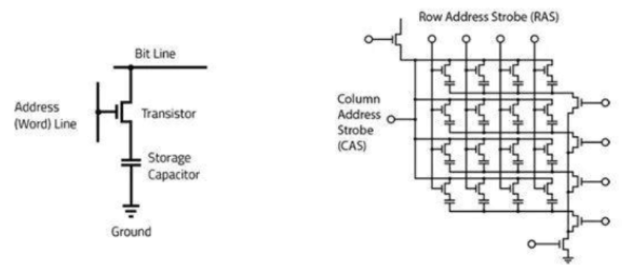

DRAM工藝提升困難的原因,主要在于它的結構。DRAM是基于一個晶體管和一個電容器的存儲單元。DRAM擴展就是在一個平面上,將每個存儲單元像拼圖一樣拼接起來。要想提升DRAM工藝,電容器的縮放是一個挑戰。另一個挑戰是電容到數字線的電荷共享,要考慮用多少時間將電荷轉移到數字線上、數字線有多長。

圖2 單個存儲單元和陣列

或許10nm并不是DRAM的極限,但是DRAM工藝提升的腳步正在放緩。人們迫切需要一個新方案,來繼續提升DRAM的性能。

在一個平面內塞入更多存儲單元很困難,那么將多個平面疊起來行不行?這就是3D DRAM,一種將存儲單元堆疊至邏輯單元上方的新型存儲方式,可以實現單位面積上更高的容量。

有哪些廠商在布局3D DRAM?

3D DRAM作為目前最被看好的下一代DRAM方案,有不少內存廠商已在布局。其中就有被大家熟知的內存巨頭——三星、美光。據BusinessKorea報道,三星今年已經開始開發一種層疊單元的技術。與高帶寬內存(HBM)不同的概念,是通過將多個模具堆疊在一起產生的。與此同時,美光也提交了一份3D DRAM的專利申請。與三星不同,美光的方法是在不鋪設單元的情況下改變晶體管和電容器的形狀。

而這次爆出的華為3D DRAM技術,據透露,是基于銦鎵鋅氧 IGZO-FET材料的 CAA 構型晶體管 3D DRAM 技術,具有出色的溫度穩定性和可靠性。

評論