5G毫米波時代的基石 —— 封裝天線技術AiP

作為收發射頻(RF)信號的無源器件,天線決定了通信質量、信號功率、信號帶寬、連接速度等通信指標,是通信系統的核心。為了進一步提升移動通信系統的容量,采用毫米波頻率進行定向通信的技術是5G預期配置的關鍵技術之一,通信頻段由6GHz以下(Sub-6GHz)提升至毫米波頻段(24GHz以上),從而通過更大的通信帶寬來提升通信系統的容量。

本文引用地址:http://www.j9360.com/article/202406/459635.htm

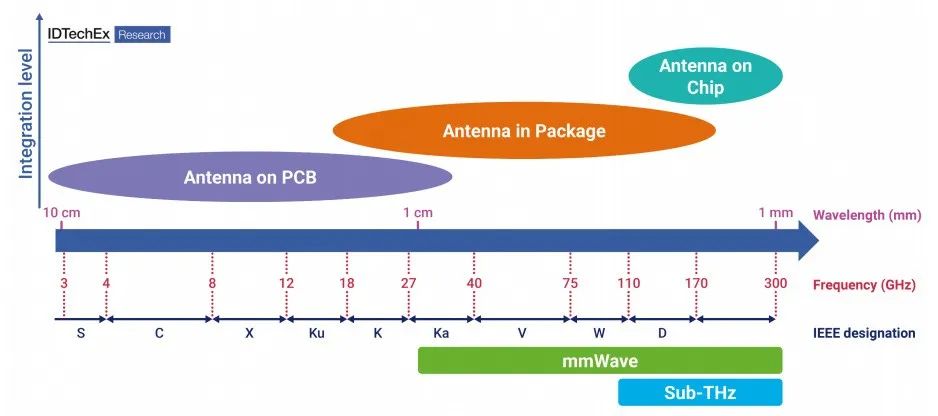

如何實現毫米波天線陣列,有兩種常見方式:AoC(Antenna on Chip)、AiP(Antenna in Package)。

更高頻率的信號就意味著更大的饋線損耗,根據測算,傳統4G手機射頻前端的饋線損耗只有1dB不到,但是在毫米波頻段線損在2-4dB,損耗比低頻率波大。由于毫米波饋線損耗大,毫米波天線不能再作為分立器件單獨設計。因此,5G時代將天線與射頻前端進一步集成就成為大勢所趨,保持輻射效率的同時縮小天線尺寸成為一項具有挑戰性的任務。

而這一集成趨勢在宏基站側就體現為基于Massive MIMO的AAU,在室分基站側就體現為由DAS向數字化室分的演進,在終端側就體現為AiP的誕生。

AoC技術于縮減天線尺寸上的效能極佳,但需經由半導體材料與制程上的統一,并與其他元件一同結合于單一芯片中,考量制造成本與芯片特性,AoC較適合應用于太赫茲(Terahertz)頻段中,因此在頻段使用與成本等因素上,其競爭力并不在毫米波頻段。

由于射頻元件大多使用GaAs為基底材料、天線多使用LCP(Liquid Crystal Polymer)為材料等,因而較適合應用于SiP技術,使得封裝天線AiP技術逐漸勝出。現階段各家芯片設計大廠(如Qualcomm)、射頻元件商(如Skyworks、Qorvo)及封測代工廠(如日月光、Amkor)等,大多選擇以AiP技術為研發方向切入5G通訊市場。

天線封裝技術與工作頻率

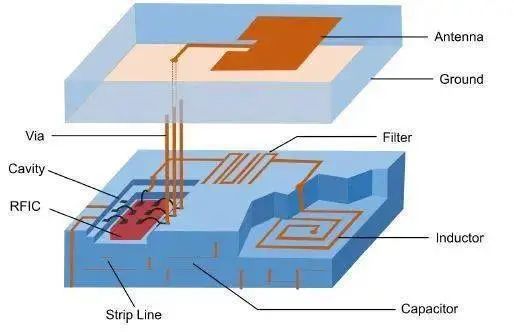

AiP技術可以說是5G毫米波頻段毫米波終端天線最適合的方案,基于封裝材料與工藝將天線、射頻收發器、射頻前端集成以及電源管理芯片集成在一起上,實現系統級無線通信模組,以減少射頻饋線帶來的損耗,實現更大的有效輻射功率。AiP技術兼顧了天線的性能、成本和體積,并具有高集成度的優勢,代表著近年來天線技術的重大成就及5G毫米波頻段終端天線的技術升級方向。

CMOS工藝把射頻芯片和數字芯片集成到一起變成SoC這一步本身就是很大的突破,SoC芯片的問世,不僅大大降低了客戶產品的開發難度,且整個系統成本也隨之下降。那么到底能下降多少成本呢?從第一代的砷化鎵到鍺硅,整個系統成本大概降了50%;到了CMOS工藝的時代,跟上一代鍺硅相比又降了40%的系統成本;而到SoC時代,又會帶來30%的成本降低。在此之上如果把天線集成到系統形成一顆AiP的SoC芯片,整個系統成本能夠進一步下探約25%,降本效果是非常明顯的。

天線尺寸與電磁波波長成正比,客觀上毫米波天線的尺寸要比低頻率天線小很多,除了手持和其他小型毫米波設備所需的小尺寸,AiP技術還能提高信號完整性,減少信號衰減,并克服高頻率所帶來的范圍和傳輸挑戰。

在從700MHz過渡到4G LTE的3.5GHz,再到5G的6-60GHz的過程當中,RF開關和頻帶復雜性以及天線設計和調試復雜性(從8x8 MIMO到68x4 MIMO)的增加是隨之出現的其中一些變化。AiP技術實現了5G所承諾的改進,在封裝層面克服很多技術挑戰。

可以說毫米波天線集成技術是實現毫米波高分辨數據流、移動分布式計算等應用場景的關鍵技術。AiP技術具有廣泛的應用,如2.4GHz的物聯網,60GHz的虛擬現實、增強現實和手勢識別,以及79GHz的汽車雷達。然而,AiP技術真正具有突破性的應用是在28GHz和39GHz的5G NR智能手機方面。綜上所述,AiP技術不再是一種選擇性技術,而是無線SoC的必選技術,將用于所有基于5G毫米波的基站和支持5G的電子產品。

5G正在全球范圍內逐步商業化,雖然截至目前,只有不到10%的商業化或預商業化5G服務基于毫米波頻段,主要部署仍然是中頻(Sub-6GHz)。但是IDTechEx在《2024-2034年5G和6G封裝天線(AiP):技術、趨勢和市場》中預測,2023年到2034年,應用于5G毫米波的AiP復合年增長率將達40.7%。在毫米波應用大放異彩的今天,AiP技術優化了毫米波性能,給予了毫米波充裕的設計靈活性,也將毫米波推向更多的應用領域。

AiP技術演進之路

AiP早期與藍牙無線技術一起發芽,由于其繼承發揚了微帶天線、多芯片電路模塊、瓦片式相控陣結構的集成概念,驅動了研究者自90年代末不斷深入探索在芯片封裝上集成單個或多個天線,這一階段的研究工作主要集中在大學實驗室,如何實現天線小型化是研究者所面臨的主要問題。

到了中期,AiP與60GHz無線技術及毫米波雷達一起成長:2010年IBM便公布了用于60GHz相控陣系統的完整AiP方案,該方案基于LTCC工藝將16個矩形微帶天線集成在BGA封裝中,發射或接收裸芯片通過倒裝焊技術與AiP相連,之后IBM進一步將其AiP的工作頻段推進到94GHz;2011年、2012年三星、Intel則分別發布了用于60GHz的相控陣系統AiP方案,同樣基于LTCC與BGA工藝;2015年谷歌首次推出了使用60GHz信號快速追蹤人手移動的手勢雷達。如今幾乎所有的60GHz無線通信和手勢雷達芯片都采用了AiP技術。

典型的AiP天線結構

AiP工藝主要有LTCC(低溫共燒結陶瓷)、HDI(高密度互聯)及FOWLP(晶圓級扇出式封裝)三種方案。基于更高的集成度、更好的散熱性、更低的傳輸損耗等優勢,并結合目前的產業化進度,FOWLP有望成為AiP天線的主流技術工藝。

FOWLP工藝不同于LTCC或HDI工藝,FOWLP不再需要疊層基片,轉而用模塑化合物、重新配置金屬與介質層代替,基于FOWLP的AiP是由英飛凌公司研發的eWLB(嵌入式晶圓級封裝)工藝發展而來。

eWLB是將裸芯片嵌入在厚度為470μm的模塑化合物中。在裸芯片的扇入區以及封裝的扇出區涂有介質層D1起到保護裸芯片的作用,D1層的厚度通常為6.5μm。重新配置的導體層(RDL)是沉積厚度為7.5μm的銅,用于實現連接線或天線。

由于eWLB工藝僅有一層金屬,不利于實現基于FOWLP的AiP。為此,臺積電開發出InFO-AiP技術,通過在模塑化合物上增加一層金屬,微帶天線輻射片由模塑化合物上面增加的金屬層實現,微帶天線地、饋線及耦合槽則在RDL金屬層實現。

FOWLP是fan-out Wafer Level Package的縮寫,其中WLP(晶圓級封裝)是以BGA(Ball Grid Array)技術為基礎,以wafer為加工對象,在wafer上同時對眾多芯片進行封裝測試,最后切割成單個器件,可直接貼裝到基板或者PCB板上的封裝方案。WLP由于不需要中介層(interposer)、填充物(underfill)與導線架,并且省略黏晶、打線等制程,因此能夠大幅減少材料及人工成本,此外,WLP大多采用RDL(重布線層)與Bumping(凸塊)技術作為I/O排線手段,因此具有較小的封裝尺寸和較佳電性表現等優勢,多應用于注重輕薄、節能的3C芯片中。

WLP可分為fan-in(標準型扇入式)及fan-out(擴散性扇出式)兩種,其中fan-in是在wafer未進行切片前對wafer進行封裝,之后再進行切片分割,完成后的封裝大小和芯片尺寸接近。而fan-out則是基于wafer重構技術,將芯片重新布局到一塊人工晶圓上,然后按照與標準的WLP工藝類似的步驟進行封裝,封裝面積大于芯片面積。傳統的WLP封裝多采用fan-in形態,應用于pin(引腳)數量較少的IC芯片,伴隨著IC引腳數目的增加,對錫球間距的要求日趨嚴格,加上PCB排線對于IC封裝后尺寸以及引腳位置的調整要求,因此衍生出fan-out。

值得注意的是,由于波長短,電路尺寸小,加工精度極其重要,傳統技術難以保證AiP模組加工精度上的一致性。采用AME技術的電路板可以實現較高的加工精度,將磁介質厚度精度控制在50um之內,金屬走線精度控制在30-40um之內,滿足對加工精度的需求。另外,AME技術可實現幾乎無限制的空間結構,可實現傳統制造技術無法實現的特殊電路結構、復雜空間構造,材料結構特性可控、加工過程可視化。可實現不同種類的基材以各種形式進行復合、堆疊,滿足對高集成度、多功能AiP實現的需求,簡化了傳統制板加工流程,降低了制造成本。

評論