看看國外廠商正在發力研究的這些新技術

但IMEC的研究人員宣稱他們找到了新的解決方法。

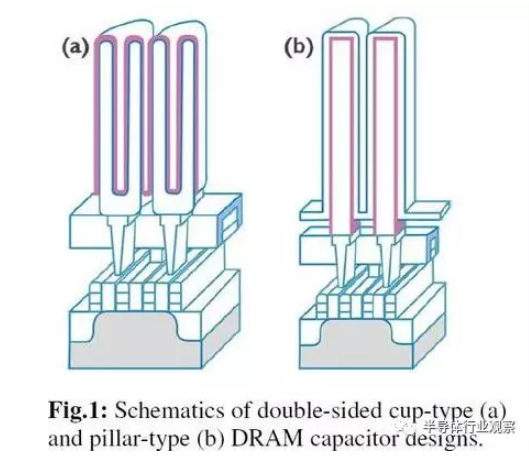

本文引用地址:http://www.j9360.com/article/201812/395988.htm首先我們先看一下其原理。所有的DRAM存儲器都包括電容器—晶體管對的陣列,他們通過充放電將其數據作為電荷存儲在電容器中;電荷的存在表示“1”,不存在時是“0”。這些數字的操作是計算機編程的基礎。但由于空間限制,使得難以在Pitch內封裝足夠的電容,因此業界難以將DRAM擴展到16nm及更小的工藝制程。

IMEC研究人員則表示,他們使用了使用新的介電材料(SrTiO3或STO),并使用原子層沉積(ALD)工藝去Pattern,打造了11nm的柱狀電容。通過調整電容器和生長它的SrRuO3(SRO)外延模板的材料特性,研究人員實現了非常高的介電常數(k~118)和低漏電(±1V時10-7 A / cm2)。這意味著可以使用柱形電容器代替現有的杯形電容器,而不會在降低數據存儲能力方面付出太多代價。這些結果使STO電容器適用于16nm和更小DRAM的持續縮放。

IBM在多個新領域的探討

普通人對于IBM的了解,就是他們曾經的PC和Power處理器,但其實過去多年來,IBM在很多先進半導體科技上的研發領先于很多廠商,在本屆的IEDM2018上,他們也帶來多個對未來技術發展的想法分享:

首先是Electrochemical Synaptic Cell。

按照IBM的說法,我們現在為神經形態計算研發的Synaptic Cell (如RRAM和PCM等非易失性存儲技術)具有非理想的切換特性(例如,不對稱的重量更新(asymmetric weight update),有限的耐用性(limited endurance)和高水平隨機性(elevated levels of stochasticity)或隨機行為(random behavior)))。

為解決這些問題,IBM研究人員將介紹一種新型可擴展電化學隨機存取存儲器(electrochemical random access memory,簡稱ECRAM)器件,該器件基于氧化鎢(WO3)中的鋰(Li)離子嵌入,可用作可擴展的synaptic cell。這些非易失性ECRAM顯示出高水平的開關對稱性和線性度,良好的數據保持能力,以及多達1,000個離散電導水平,這可用于大型存儲器陣列中的多級操作。

研究人員還展示了這個器件成功的高速編程能力。他們使用5ns脈沖寬度和300x300nm2 ECRAM器件。對于縮放的100x100nm2器件,預計具有1 fJ的超低開關能量。基于實驗數據的MNIST圖像識別模擬顯示96%的準確度。

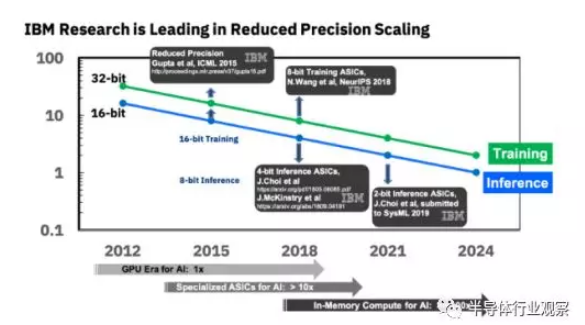

其次,解決內存計算的主要挑戰;

李飛在文章《內存內計算,下一代計算的新范式?》中說到了“內存墻”問題,而IBM在IEDM 2018上帶來了解決基于PCM內存內計算的一個大挑戰——“精度有限”。他們提出了一種設備級解決方案,也就是他們所說的Proj-PCM。

據介紹,這個方案可以實現AI相關計算所需的標量乘法數學(scalar multiplication mathematics)的高精度(8位)和低功率(60 nW)。相變材料是高度非線性的,新穎的Proj-PCM器件采用所謂的projection segment(金屬電阻器),以便在讀取存儲器時穩定材料的電導(electrical conductance),從而降低噪聲和溫度漂移。他們構建了一個用于圖像識別的單層神經網絡,包括30個Proj-PCM設備并對其進行離線訓練,之后即使在高溫下也能表現出無差錯的模式識別性能。

這個方案具有存儲和處理數據的雙重功能,其單獨的架構調整可以將能耗降低90%以上,并且相變存儲器(PCM)可以獲得額外的性能提升。該屬性使其能夠執行計算,研究人員預測的PCM(Proj-PCM)使PCM在很大程度上不受電導變化的影響,從而實現比以前更高的精度。按照論文介紹,這個方案不但能夠以 8-bit 精度訓練深度學習模型,同時保持圖像、速度、文本數據集類別的模型精度。

除此之外,IBM還在探索用III-V族材料代替Si溝道材料的方法。

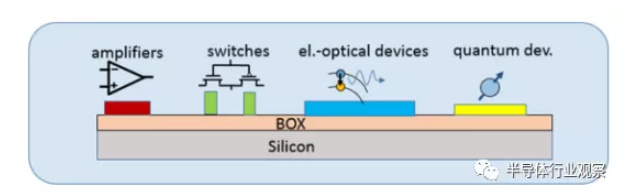

他們表示,III-V材料提供了硅沒有的幾個優點:如較低的有效質量,較高的遷移率和直接的帶隙,這使它們更適合光子和隧道器件。硅已經并將繼續成為電子行業的首選半導體,因為Si豐富,低成本,堅固并且在高質量SiO 2氧化物方面提供理想的鈍化。為了結合兩者的優點,在Si上集成III-V材料具有很高的技術和經濟意義,并且已經被追求了多年。

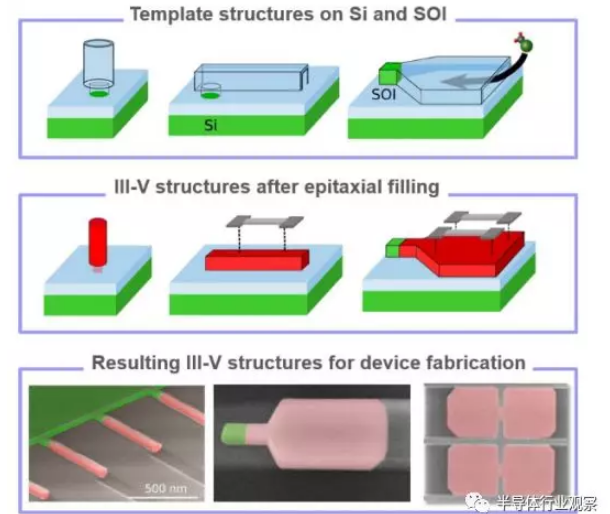

如下圖所示,與基于Si的電路緊密“聯系”的III-V器件可以提高系統性能,甚至可以實現新的應用領域,預期其系統制造成本將顯著低于分立芯片封裝方法。

Si上III-V材料和器件的各種應用空間的示意圖

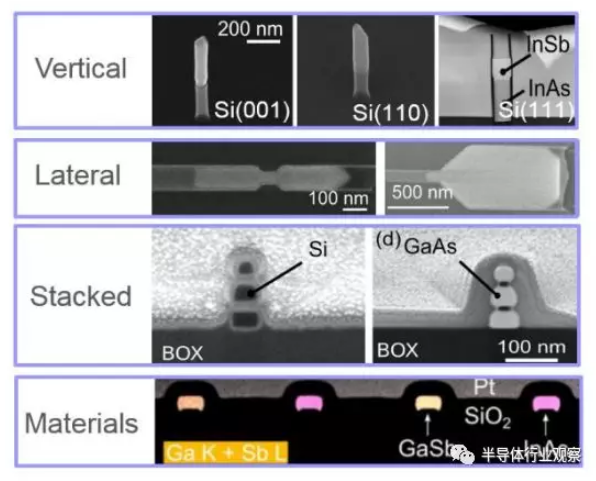

他們開發了一種新的外延生長方法,在在Si上沉積III-V材料,從而獲得良好的材料質量。最重要的一點是,該工藝與CMOS工藝兼容,這就是他們所謂的“模板輔助選擇性外延”(Template-Assisted-Selective-Epitaxy,縮寫TASE)工藝。

據介紹,IBM的這個工藝設計是為了將高遷移率材料集成成納米級別的sheets而設計的,他們也Si上集成了高性能InGaAs GAA nanosheet N-FETs。據報道,Nanosheets的厚度可以做到10nm,晶體管的柵極長度小于40nm,且柵極金屬環繞通道,以實現最佳的柵極控制。

Si上集成三五族材料的范例

這些器件具有出色的電流驅動能力(Ion =355μA/μm),以及72 mV / decade的亞閾值擺幅(subthreshold swing)。研究人員表示,通過縮放柵極長度/nanoshee尺寸可以進一步提高器件性能,且這些器件與當前的硅制造工具兼容。

Template-Assisted-Selective-Epitax

在這場大會上,還有量子計算、無線通信、寬帶系功率電子和存儲等多方面的分享。正是在一代代研究人員的努力下,我們才有了今天的電子世界。相信更美好的未來值得期待。

評論