半導體芯片如何實現“瘦身之路”?3D IC是一大絕招

3D芯片級測試品質意味著什么?

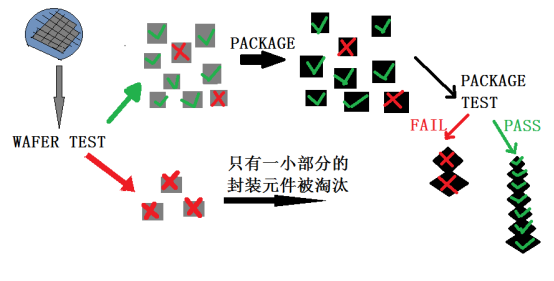

本文引用地址:http://www.j9360.com/article/201811/394022.htm在進行3D測試之前,晶圓首先要經歷晶圓測試;有些芯片可通過測試,另一些則否。通過測試的裸晶繼續進行封裝,然后進行封裝測試,在這些環節還會發現更多不合格件。

1、傳統晶圓和封裝測試的比較

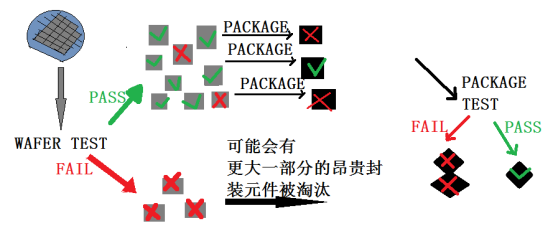

2、3D堆疊IC的晶圓與封裝測試比較

如果裸晶缺陷覆蓋率是95%,則10層芯片堆疊的最終封裝良率將會是60%。顯然地,如果5%的逃脫率導致40%的最終產品被丟棄,這并不是我們希望看到的。

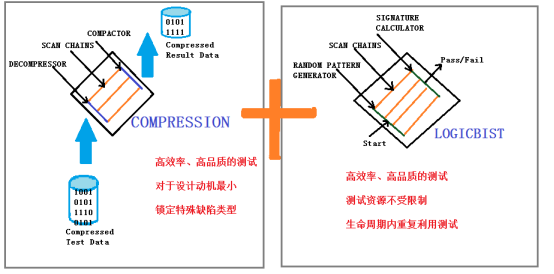

3、嵌入式測試壓縮和邏輯內建自測試組合的優點

3D封裝需要非常高品質的晶圓級測試,以便只有“良品裸晶”被封裝在一起。3D測試還需要已知合格的中介層、部份堆疊測試、TSV和封裝測試。

邏輯內建自測試元件使系統自我測試成為可能,這對于汽車或醫療應用的IC尤為重要。添加單元內和非傳統失效模型則能夠使設計中數位邏輯元件的測試品質達到可接受的程度。除此之外還需要測試嵌入式IP、I/O以及TSV。

對于I/O和TSV,因為無法保證與ATE的電氣接觸,測試必須在非接觸形式下進行。這是一個有待研究的領域;其中一種有趣的做法是使用邊界掃描途徑,為部份封裝的元件進行晶圓級測試,以及封裝內芯片之間的互連測試。

總結:

未來幾十年內,3DIC都將憑借著更低的成本、更小的體積,以及推動芯片功能進化等優勢,成為未來半導體產業的新典范,而3D堆棧DRAM和3D邏輯SoC應用將成為推動3DIC技術獲得大量采用的最主要驅動力,接下來依序是CMOS影像傳感器、功率組件和MEMS等。所謂的wide I/O接口以及在28nm采用TSV技術來大量制造移動/平板產品專用應用處理器芯片的情況也將有可能發生。但事實上,要成功推動3DIC,除了技術問題,還涉及到復雜的供應鏈部份,它要改變的層面非常多。因此,包括三星和臺積電(TSMC)在內的晶圓代工巨擘們,都不停針對3DIC展開垂直整合布局,希望能滿足領先無晶圓廠半導體公司,如高通、博通、Marvell、NVIDIA和蘋果的需求,以及其它采取輕晶圓廠策略的業者如德州儀器、意法半導體和NEC /瑞薩等。

未來在拓展3DIC業務時,業界必須尋求所謂的“虛擬IDM”模式,其中包括TSV蝕刻填充、布線、凸塊、晶圓測試和晶圓級組裝在內的中階晶圓處理部份,有報告指出,其市場規模預計可達38億美元。另外,后段的組裝和測試部份,如3DIC模塊等,預估將達46億美元,而這些,都代表著先進封裝產業未來可持續獲得成長的商機所在。

評論