基于FPGA的基帶64×64 數據分配矩陣設計方案

本文采用FPGA作為實現控制邏輯的核心部件,提出了基于FPGA的基帶64×64 數據分配矩陣設計方案,并介紹了上位機的軟件設計思路和FPGA的內部編程實現及仿真。經驗證該方案具有規模大、成本低、高速等特點,可廣泛應用于大規模基帶數字系統測試及信號程控分配調度中。

本文引用地址:http://www.j9360.com/article/201809/388651.htm0 引言

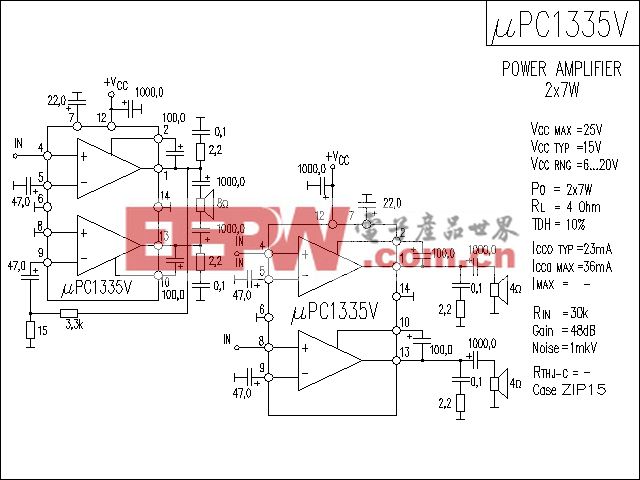

數據分配矩陣即矩陣開關,顧名思義,指結構為行列交叉排布的開關產品,其特點為每個節點連接一個行/列,每個節點可以單獨操作,通過設置節點的不同組合可以實現信號的路由。矩陣開關的主要優勢在于其簡化的部線,整個測試系統可輕松地動態改變其內部連接路徑而無須外部手動干預。矩陣開關的使用非常靈活方便,是目前程控開關產品中品種最多的產品,在汽車電子、半導體測試、航空航天等領域得到了廣泛的應用。

FPGA具有運行速度快,內部邏輯資源豐富,外圍I/O口數量多等優點,因此本設計選用FPGA作為核心器件。

1 系統結構及功能

本設計是為了實現64位輸入信號到64位輸出的任意無交叉的切換,即輸入與輸出是一一對應的。由于本設計是針對基帶數字信號,而設計中選用的晶振頻率為25 MHz,因此根本不用考慮FPGA處理異步時鐘域數據傳輸的問題,只需直接將對應的輸入信號經電平轉換后,經譯碼后直接輸出到相應的某路輸出接口即可。

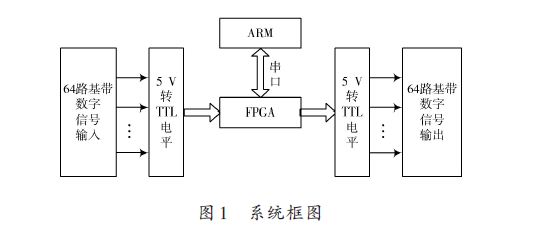

上位機ARM 通過串口向FPGA 發送接口的連接信息,FPGA根據接收到的數據進行譯碼,將對應的輸入與對應的輸出連接起來,實現規定鏈路的連接。考慮到所含資源以及管腳數量,本設計方案選用Altera公司Cyclone Ⅲ系列EP3C25F256型FPGA.選用了4塊32路的電平轉換芯片實現5 V 信號向FPGA 能夠識別的TTL 信號的轉換。

其結構框圖如圖1所示。

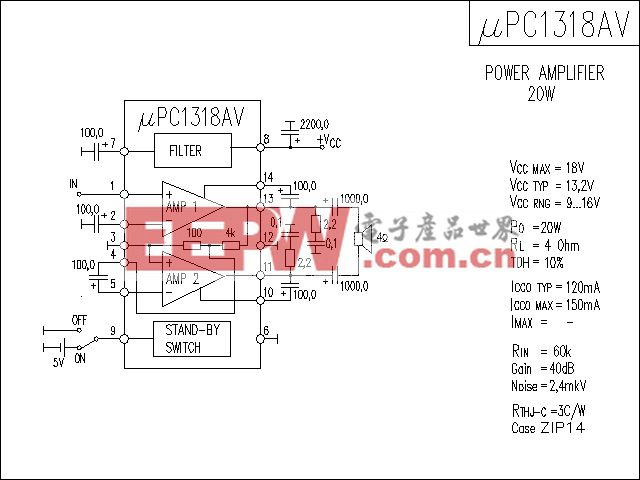

2 上位機設計

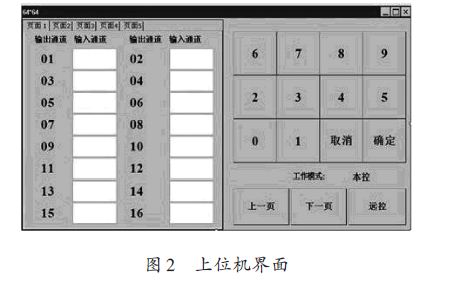

上位機的界面如圖2 所示。在相應的輸入通道文本框里輸入0~64,點擊“確定”按鈕后,首先對文本框里所有的數據進行比較判斷,如出現重復則進行報錯,提示重新輸入。無誤后,通過串口按輸出接口順序依次向FPGA發送64條接口的連接指令。每一條指令包含3 B,第一個字節為信息頭“AA”,若FPGA接收到的某條指令的頭字節不是“AA”,則無返回信息,上位機將重新發送這條指令直到正確為止。第二個字節為輸入端口字節,即對應文本框中的數字,如沒有輸入數字則默認發送0,所以如需端口某條鏈路斷開只要在相應的文本框中輸入0,點擊確定即可。第三個字節為輸出端口對應的數據,按1到64順序發送。圖2中的“遠控”按鈕為預留的用作計算機遠控使用。

3 下位機設計

3.1 串口通信協議

串行通信是一種可以將接收到的并行數據字符轉換為連續的串行數據流發送出去,同時可將接收的串行數據流轉換為并行的數據字符發送出去的通信協議。

其數據幀主要包括1位起始位,8位數據位,1位奇偶校驗位,1/2位停止位。

3.2 FPGA內部編程

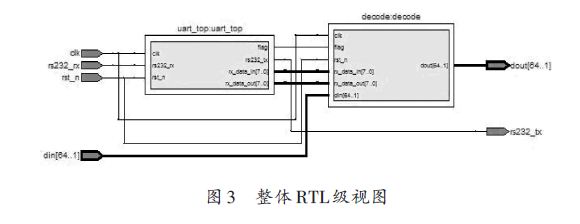

FPGA模塊的主要功能是實現串口收發和譯碼,相應地在用Verilog HDL實現時也分為串口收發和譯碼2個電路模塊,經綜合后其RTL級視圖如圖3所示。開發工具采用Altera公司推出的集成EDA 開發工具Quartus Ⅱ,可以完成Altera公司所有的FPGA /CPLD產品開發的設計輸入、綜合、實現等環節。

3.2.1 串口收發模塊設計

串口收發模塊就是圖3中的uart_top模塊,主要負責串行數據的接收與發送,并將接收到的數據送入下一級。

該模塊的功能已通過串口調試工具調試成功。該模塊由4個子模塊構成,分別為控制接收波特率的speed_rx模塊、控制發送波特率的speed_tx 模塊、數據接收模塊my_uart_rx、數據發送模塊my_uart_tx.

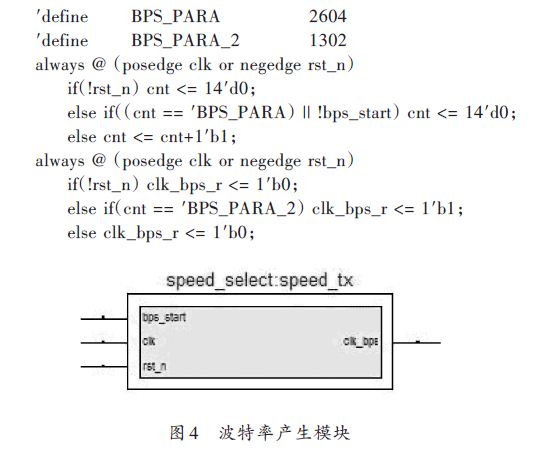

接收、發送波特率的控制可以引用同一模塊的發送來實現。其模塊化框圖如圖4所示,當檢測到輸入信號bps_start出現一個上升沿后,則該模塊通過計數來實現分頻,例如時鐘頻率為25 MHz,波特率為9 600,則計數周期的25 000 000/9 600≈2 604,該模塊部分代碼如下:

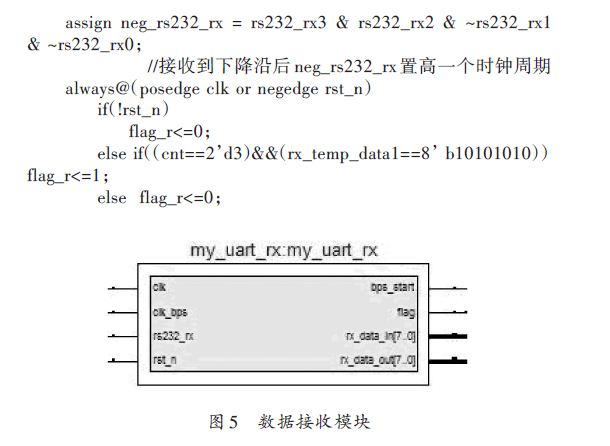

數據接收模塊的模塊化框圖如圖5所示,它是通過移位運算來接收串行數據,如檢測到rs232_rx由高電平變為低電平則開始移位接收數據,每次接收3 B 的數據,將第二、第三個字節輸入下一級,若檢測到第一個字節為10101010(即16進制的AA),標志信號flag就將維持一個周期的高電平輸出,否則flag一直維持高電平,那么后級將無法鎖存第二、第三字節。部分代碼如下:

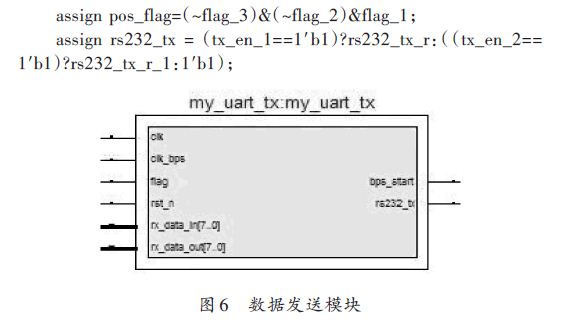

數據發送模塊是用來返回接收數據讓上位機進行糾錯的,其模塊化框圖如圖6所示。如檢測到flag變為高電平時,鎖存輸入的兩個字節返回給上位機,部分代碼如下:

3.2.2 譯碼模塊設計

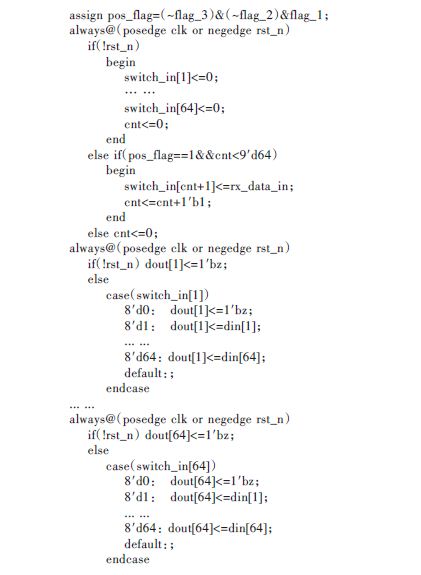

譯碼模塊的模塊化框圖如圖7所示,其功能是對上位機發送的輸入輸出端口編號進行譯碼,使相應的輸入端口和輸出端口連通,如檢測到flag 有效的情況下,rx_data_in為2,rx_data_out為3,則該模塊會將din[2]通道的輸入信號經dout[3]輸出通道輸出。部分代碼如下[10]:

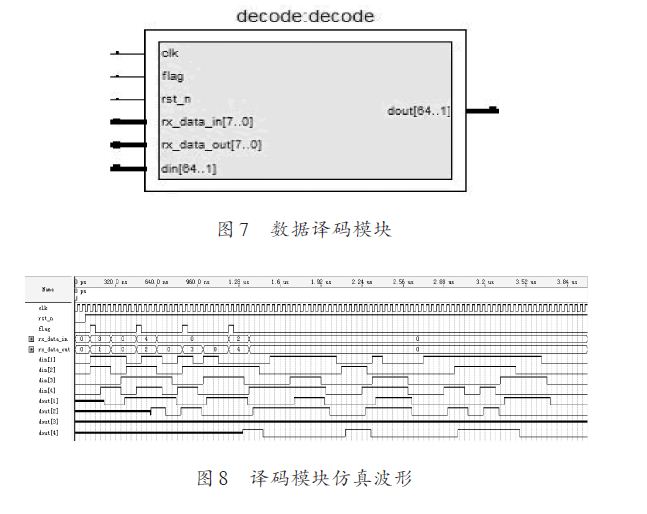

3.2.3 譯碼模塊仿真

由于64×64的仿真很繁瑣且不易操作,所以對4×4的譯碼模塊進行仿真,仿真結果如圖8所示,輸出1與輸入3相連,輸出2與輸入4相連,輸出3懸空,輸出4與輸入2相連。

4 結語

本文采用FPGA作為實現控制邏輯的核心部件,提出了基于FPGA的基帶64×64 數據分配矩陣設計方案,并介紹了上位機的軟件設計思路和FPGA的內部編程實現及仿真。經驗證本系統基本能實現基帶數字信號的分配路由,從而證實了該方案具有規模大、成本低、高速等特點,可廣泛應用于大規模基帶數字系統測試及信號程控分配調度中。

評論