常用EDA工具之Tanner

集成電路版圖編輯器L-Edit(Layout-Editor)在國內已具有很高的知名度。 Tanner EDA Tools 也是在L-Edit的基礎上建立起來的。

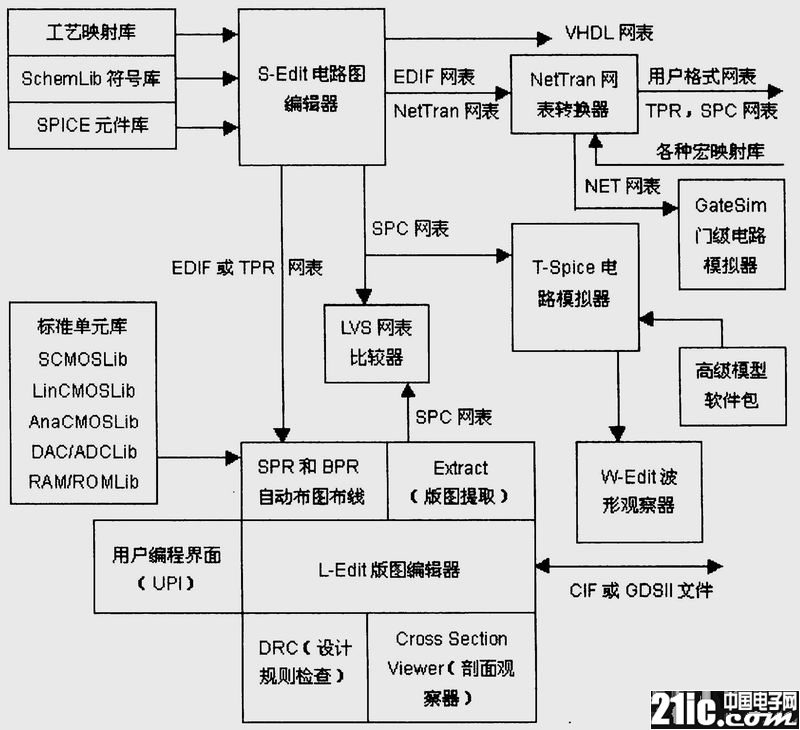

本文引用地址:http://www.j9360.com/article/201808/385701.htm整個設計工具總體上可以歸納為電路設計級和版圖設計級兩大部分。

即以S-Edit為核心的集成電路設計、模擬、驗證模塊和以L-Edit為核心的集成電路版圖編輯與自動布圖布線模塊。

電路設計級包括電路圖編輯器S-Edit、電路模擬器T-Spice和高級模型軟件、波形編輯器W-Edit、NetTran網表轉換器、門電路模擬器GateSim,以及工藝映射庫、符合庫SchemLib、Spice元件庫等軟件包,構成一個完整的集成電路設計、模擬、驗證體系,每個模塊互相關聯又相對獨立,其中S-Edit可以把設計的電路圖轉換成SPICE,VHDL,EDIF和TPR等網表文件輸出,提供模擬或自動布圖布線。

版圖設計級包括集成電路版圖編輯器L-Edit和用于版圖檢查的網表比較器LVS等模塊。

L-Edit本身又嵌入設計規則檢查DRC、提供用戶二次開發用的編輯界面UPI、標準版圖單元庫及自動布圖布線 SPR、器件剖面觀察器 Cross Section Viewer)版圖的SPICE網表和版圖參數提取器Extract(LPE)等。

網表比較器LVS則用于把由L-Edit生成的版圖反向提取的SPC網表和由S-Edit設計的邏輯電路圖輸出的SPC網表進行比較實現版圖檢查、對照分析。

L-Edit除了擁有自已的中間圖形數據格式(TDB格式)外,還提供了兩種最常用的集成電路版圖數據傳遞格式(CIF格式和GDSII格式)的輸入、輸出功能,可以非常方便地在不同的集成電路設計軟件之間交換圖形數據文件或把圖形數據文件傳遞給光掩模制造系統。

Tanner集成電路設計中的各種CAD工具

Tanner Pro是一套集成電路設計軟件,包括S-Edit,T-Spice,W-Edit,L-Edit與LVS。缺少NetTran和GateSim。

軟件 | 功能 |

S-Edit | 編輯電路圖 |

T-Spice | 電路分析與模擬 |

W-Edit | 顯示T-Spice模擬結果 |

L-Edit | 編輯布局圖、自動配置與布線、設計規則檢查、截面觀察、電路轉化 |

LVS | 電路圖與布圖結果對比 |

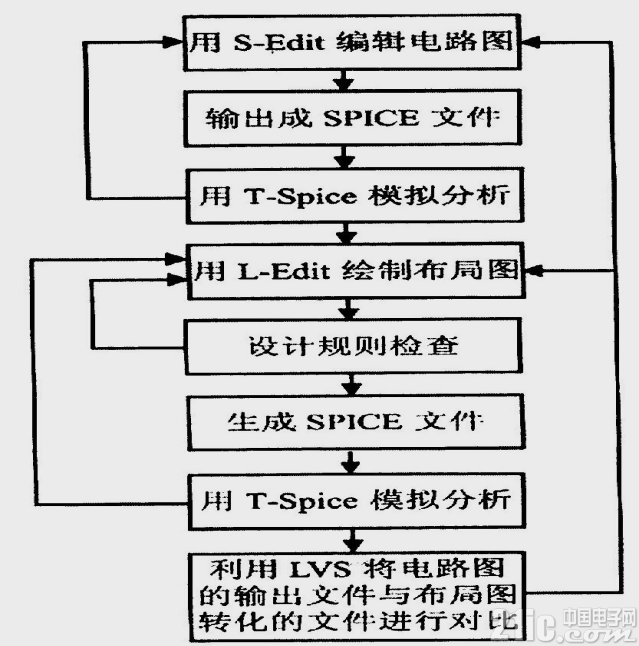

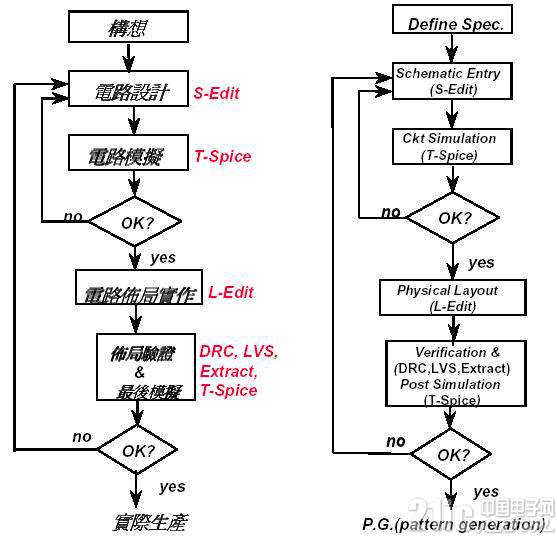

首先用S-Edit編輯要設計電路的電路圖,再將該電路圖輸出成SPICE文件。接著利用T-Spice將電路圖模擬并輸出成SPICE文件,如果模擬結果有錯誤,再回S-Edit檢查電路圖,如果T-Spice模擬結果無誤,則以L-Edit進行布局圖設計。用L-Edit進行布局圖設計后要以DRC功能做設計規則檢查,若違反設計規則,再將布局圖進行修改直到設計規則檢查無誤為止。將驗證過的布局圖轉化成SPICE文件,再利用T-Spice模擬,若有錯誤,再回到L-Edit修改布局圖。最后利用LVS將電路圖輸出的SPICE文件與布局圖轉化的SPICE文件進行對比,若對比結果不相等,則回去修正L-Edit或S-Edit的圖。直到驗證無誤后,將L-Edit設計好的布局圖輸出成GDSII文件類型,再交由工廠去制作半導體過程中需要的的光罩。

評論