高壓靜電除塵器中振打控制電路的EDA設計

0 引言

本文引用地址:http://www.j9360.com/article/201807/384374.htm隨著國家對煙氣排放要求越來越嚴格,電除塵器技術已被廣泛應用并取得很大進展。振打控制是電除塵器的基本功能之一,是實現“全自動控制”不可或缺的環節。對整個靜電除塵器的啟動、停止、緊急停機功能一般系統都能做到,但其間程序繁多,且出現問題不易修改,使得無法更好地將振打的理論效果較好體現于實踐中。

文中設計了一種新型電除塵器振打控制電路,利用EDA(電子設計自動化)技術,采用先進的VHDL硬件電路描述語言,使得盡管目標系統是硬件,但整個系統的設計和修改如同對軟件作用一樣方便和高效。

1 電路設計原理

智能型振打控制要求振打及時且不引起二次揚塵。此處設計的振打控制器,可以實現準確控制振打電路的通斷,并根據實際需要設置振打間隔周期,以及每次振打的時間等。由現場測量得知,電除塵器的振打要求是:電源接通后,系統先進行一次20S的振打,經過延時一定周期—40min后,再進行20S的振打,周而復始,以保證電除塵器的正常運行。這個環節的主要組成部分是一個脈沖發生器,文章是通過控制脈沖波形,來實現周期的一定性和每次振打時間的準確性。

2 20S的延時振打電路

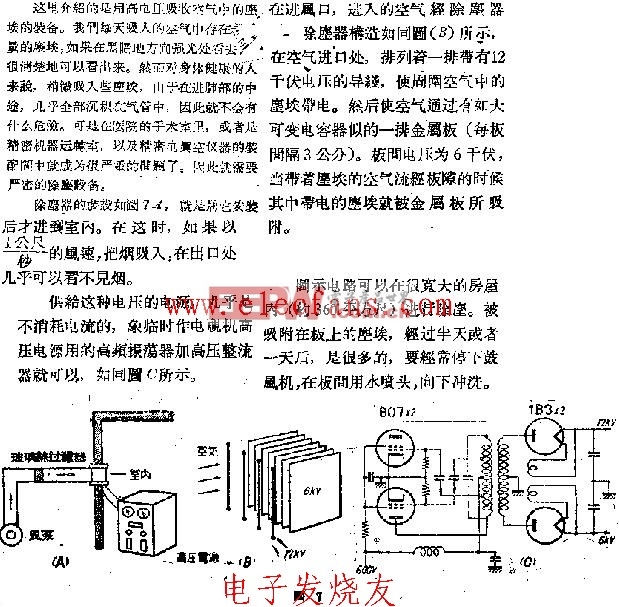

對于20S延時振打電路,是通過由CC555構成的單穩態電路來實現。單穩態觸發器只有一個穩定狀態和一個暫穩態,在外界觸發脈沖的作用下,電路從穩態翻轉到暫態,然后在暫態停留一段時間Tw后又返回到穩態。此處暫態控制20S的延時振打。延時振打時間Tw只與元件R和C的參數有關。要使Tw=20s,只需令C=lOOuF,R=200k。電路如1所示。

圖1 20S的延時振打原理圖

3 40min周期控制的電路

對于20S周期的系統,要將其轉化為40min,采用由七個D觸發器構成的二分頻計數器來實現,二分頻的結果是頻率降低一半,周期增加一倍,即初始周期為20S,經過7個二分頻器后,其周期依次變為40S、80S、160S、320S、640S、1280S、2560S。

第1個D觸發器的輸入時鐘為需要分頻的系統時鐘,將該D觸發器的輸出取反做該觸發器的輸入;第2個觸發器的時鐘為第1個D觸發器的輸出,將第2個D觸發器輸出取反作其輸入,依此類推。

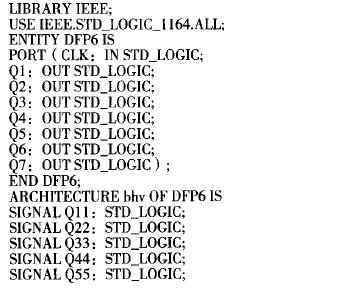

40min周期控制的VHDL代碼及仿真波形

電路七次分頻(即1280S變2560S)的VHDL代碼:

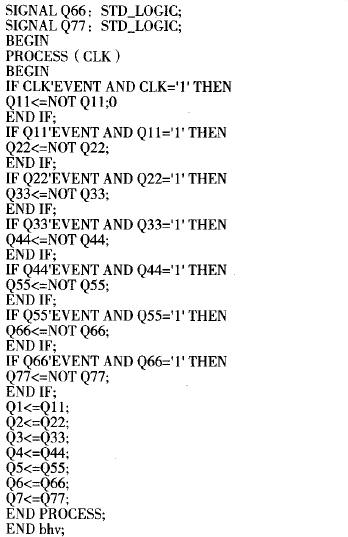

仿真波形如2所示。

圖2 七次分頻仿真波形

4 結束語

通過7個連續的D觸發器和555單穩態觸發器分別實現40min的振打周期和20s的延時振打。此設計可以嚴格控制,調節振打時間。對于不同性質的粉塵,可通過修改VHDL程序及參數設置對所設電路的調整,實現針對性振打。經過QuatusⅡ仿真,所示各項指標均符合設計要求,從而驗證了該設計方案的正確性與可行性。

評論