EUV微影前進7nm制程,5nm仍存在挑戰

EUV微影技術將在未來幾年內導入10奈米(nm)和7nm制程節點。 不過,根據日前在美國加州舉辦的ISS 2018上所發布的分析顯示,實現5nm芯片所需的光阻劑仍存在挑戰。

本文引用地址:http://www.j9360.com/article/201801/374846.htm極紫外光(extreme ultraviolet;EUV)微影技術將在未來幾年內導入10奈米(nm)和7nm制程節點。 不過,根據日前在美國加州舉辦的年度產業策略研討會(Industry Strategy Symposium;ISS 2018)所發布的分析顯示,實現5nm芯片所需的光阻劑(photoresist)仍存在挑戰。

同時,EUV制造商ASML宣布去年出貨了10臺EUV系統,今年將再出貨20至22臺。 該系統將擁有或至少可支持每小時生產125片晶圓所需的250W雷射光源。

IC Knowledge總裁Scotten Jones表示:「在7nm采用EUV的主要部份已經到位,但對于5nm來說,光阻劑的缺陷仍然高出一個數量級。 」

經過20多年的發展,新的和昂貴的系統均有助于為下一代芯片提供所需的優質特性,并縮短制造時間。 Scotten說,這些系統將首先用于制造微處理器等邏輯芯片,隨后再應用于DRAM,但現今的3D NAND閃存芯片已經不適用了。

「EUV大幅減少了開發周期以及邊緣定位的誤差...,但成本降低的不多,至少一開始時并不明顯。 此外,還有其他很多的好處,即使沒什么成本優勢,它仍然具有價值。 」

Jones預計,ASML將在2019-2020年之間再出貨70臺系統。 這將足以支持在Globalfoundries、英特爾(Intel)、三星(Samsung)和臺積電(TSMC)規劃中的生產節點。

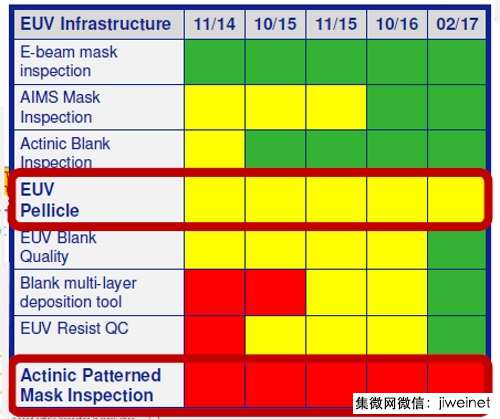

除了EUV系統本身,其他重要的挑戰還包括薄膜、光罩測試儀和抗蝕劑(來源:ASML)

Jones表示,ASML計劃將系統的正常運行時間從現在的75%提高到90%,這同時也是微影技術業者最關切的問題。 此外,他表示相信該公司將會及時發布所需的薄膜,以保護EUV晶圓避免微塵的污染。

為了開發針對5nm可用的抗蝕劑,「我們有12到18個月的時間來進行重大改善。 業界將在明年產出大量晶圓,這將有所幫助。 」Jones并估計,到2019年晶圓廠將生產近100萬片EUV晶圓,到了2021年更將高達340萬片晶圓。

ASML的目標是在2020年時,將其250W光源所能達到的每小時145片晶圓的吞吐量提高到155片/時。 ASML企業策略和營銷副總裁Peter Jenkins在ISS上指出,該公司已經展示實驗室可行的375W光源了。

目前該公司的薄膜已經能通過83%的光線了,至今也以245W光源進行超過7,000次的晶圓曝光測試了。 然而,第二代7nm節點在搭配用于250W或更高的光源時,預計還需要一個傳輸率達到90%的薄膜。

GF、英特爾、三星與臺積電的7nm版本

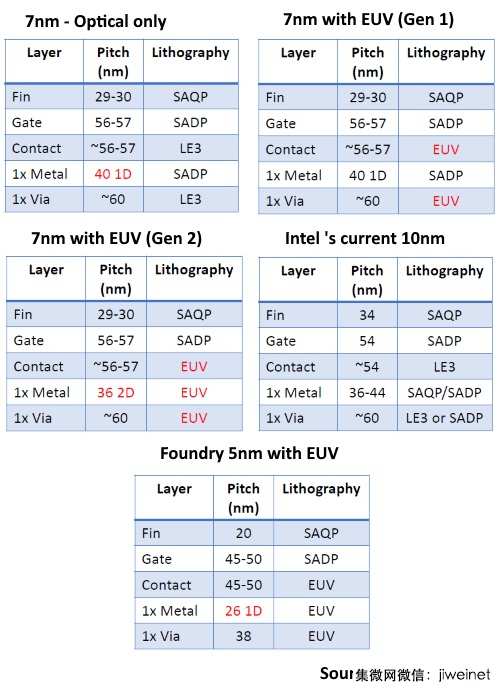

Jones談話中最有趣的部份內容就是對于10nm、7nm和5nm節點的詳細分析。 臺積電去年秋天通過7nm制程,目前正使用現有的光學步進器實現量產。 他說,Globalfoundries將在今年晚些時候推出類似的制程。

兩家公司計劃在明年初量產第二代7nm制程,采用EUV制作觸點和通孔,將15個光學層數減少到5個EUV層。 這一制程可望縮短周期時間,而且不需要薄膜。

Globalfoundries去年六月份宣布在2019年采用EUV實現7nm的計劃。 Jones「臺積電私下告訴客戶也計劃如此。 」瓊斯說。

芯片制造商可能必須使用30mJ/cm2劑量的抗蝕劑,這高于其目標的20mJ/ cm2。 他們還可能必須使用電子束系統檢查光罩的缺陷,而不是像EUV系統一樣使用13.5mm波長尋找缺陷的光化系統。

Globalfoundries、三星和臺積電除了使用觸點和通孔外,還計劃為不同的7nm版本使用EUV和薄膜來制作1x金屬層。 這些制程將提供微縮,并使23層光學層減少到9層EUV。

這正是三星將在明年初推出的首款7nm節點,即7LPP。 臺積電的7FF+版本,預計將在2019年中期推出,Globalfoundries則將在明年年底推出7LP+。

Jones詳細介紹了他預計到2020年將會看到的各種10nm、7nm和5nm制程版本

Jones表示,英特爾目前使用的10nm制程采用光學步進器實現量產,提供的密度相當于其競爭對手所能實現的最佳7nm版本。 他預期英特爾將在2019年采用EUV升級10nm+制程。

三星和臺積電已經在討論可能在2019年底前提供5nm制程。 他們應該會是第一批使用EUV制造1D金屬層的制造商。 他說,如果有更好的抗蝕劑出現,這個制程就能使用EUV減少多達5個切割光罩,讓FinFET減少到僅使用1個光罩。

另外,Jenkins表示,ASML已經為支持高數值孔徑(NA)的EUV系統完成光學設計部份了,而且整體設計「順利」。 該公司已于2016年底宣布計劃在2024年量產該新系統。

盡管EUV是推動半導體產業制造更小芯片的重要里程碑,但預計并不至于顛覆目前的芯片制造設備和裝置市場。 Jones說,晶圓廠將會持續需要大量的現有資本設備和供應,才能與EUV一起邁向未來的制程節點。

評論