以太網收發電路設計方案詳解

以太網收發電路由RJ45接口、耦合變壓器、以太網收發器,以及收發器與調制驅動電路、接收解調電路之間的接口組成。其中以太網收發器是核心單元,直接決定了系統的工作性能。以太網收發器IP113IP113是二端口10/100Mbps以太網集成交換器,由一個二端口交換控制器和兩個以太網快速收發器組成。每個收發器都遵守IEEE802.3、IEEE802.3μ、IEEE802.3x規則。為幀緩沖保留了 SSRAM,可以存儲1K字節的MAC地址,全數字自適應調整和時序恢復,基線漂移校正,工作在10/100baseTX 和100baseFX的全雙工/半雙工方式。使用2.5V單電源,25MHz單時鐘源,0.25μm工藝,128腳PQFP封裝。

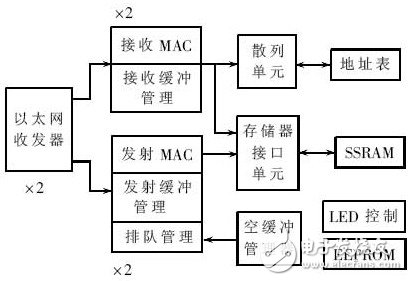

本文引用地址:http://www.j9360.com/article/201710/369341.htmPort1的速率是自適應調整的結果,因而不需要外加存儲器以緩沖數據包。每個端口都有自己的接收緩沖管理、發射緩沖管理、發射排隊管理、發射MAC和接收MAC。各個端口共享一個散列單元、一個存儲器接口單元、一個空緩沖管理器和一個地址表。

圖2 IP 113內部原理框圖

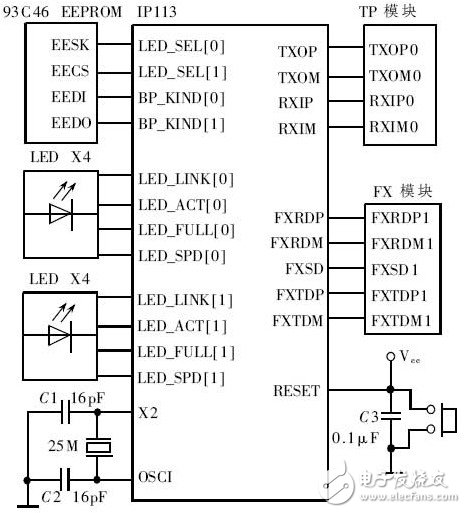

主要由以太網收發芯片IP113、專用配置芯片EEPROM 93C46、LED顯示矩陣,以及IP113的Port1與TP模塊、Port2與FX模塊之間的接口組成。 IP113支持很多功能,通過設置適當的參數滿足不同的需要,既可以由特定的管腳設定,也可以用EEPROM配置。為提高系統的整體性能,這里采用專用串行EEP ROM 93C46芯片。系統復位時,管腳LED_SEL[1:0]分別作為93C46的時鐘EESK和片選EECS,BP_KIND[1:0]分別作為 93C46地址EEDI和數據輸出EEDO,將93C46內部的參數讀入IP113內部的寄存器。復位結束后,這些管腳均變成輸入信號,以使IP113脫離93C46而獨立工作。

圖3 以太網收發電路

復位時,IP113首先讀取93C46的00H中的內容,只有00H[15:0]=55AAH時,才會繼續從EEPROM中讀取參數,否則以缺省值或特定的管腳電平值設置工作寄存器。01H中的值設置LED輸出控制寄存器,控制兩個LED矩陣的亮、滅和閃爍,以分別顯示兩個端口的連接、活動、全/半雙工和速率(10Mbps/100Mbps)。02H中的值設置交換控制寄存器1,選擇系統的流控制方式和沖突保護。03H中的值設置交換控制寄存器2,控制系統的丟包、地址失效、優先級和算法補償。04H中的值設置收發器控制寄存器,其中04H[13:11]的5 種取值:000、100、101、110和111,分別對應收發器的5種工作狀態:NWAY、10Mbps(半雙工)、10Mbps(全、半雙工)、 100Mbps(半雙工)和100Mbps(全、半雙工)。05H~0AH中的值分別設置收發器確認寄存器、測試寄存器和驗證方式寄存器。

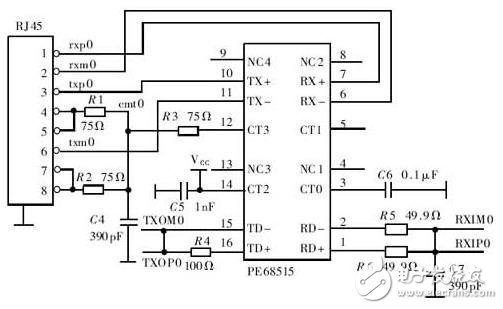

Port1的TXOP和TXOM是TP發射數據對,RXIP和RXIM是TP接收數據對。圖4的TP模塊電路中,RJ45接口將MLT-3碼流以太網信號經過耦合脈沖變壓器PE68515變為單極性信號。

圖4 IP模塊電路圖

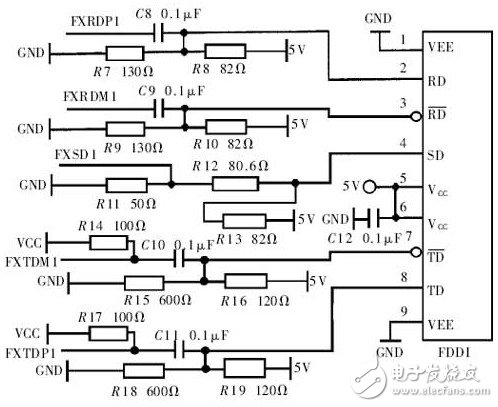

Port2的FXRDP和FXRDM是FX的接收數據對,FXTDP和FXTDM是FX的發射數據對。FXSD是光電檢測信號,當接收到的光信號經光電轉換后電平低于1.2V時,FXSD輸出連續的PECL電平。圖5是FX模塊的電路圖,電路中采用標準的FDDI數據接口。由于調制驅動和接收解調電路采用5V電源,而系統其它部分均使用2.5V電源,FDDI中的信號均是PECL電平,因此必須經電平轉換(如圖5所示),才能把這兩部分聯系起來。

圖5 FX模塊電路圖

----------------------------------------

智能家電技術資料集錦——讓家電設計邁入嶄新時代!

評論