多核處理器會取代FPGA嗎?

有人認為諸如圖形處理器(GPU)和TIlera處理器等多核處理器在某些應用中正逐步替代現場可編程門陳列(FPGA)。理由是這些多核處理器的處理性能要高很多,例如,由于GPU起初主要負責圖形繪制,因此,其尤其善于處理單精度(SP)及(某種情況下)雙精度(DP)浮點(FP)運算。TIlera的TILE設備當前不支持硬件FP運算,但要求進行軟件模擬,且性能代價高昂。一般而言,FPGA亦是如此,設備通過利用多種資源來處理FP運算問題。達到可接受性能要求IP區塊需消耗多個門并要求深流水線技術。例如:當前Tesla級GPU每秒最高可執行1012次浮點運算或1TFLOPS,而Xilinx Virtex-6設備則為150 GFLOPS。

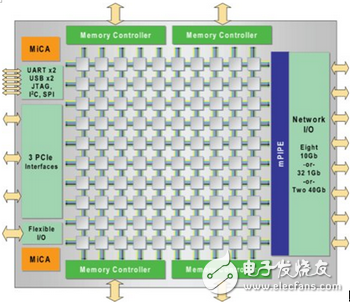

本文引用地址:http://www.j9360.com/article/201710/365672.htm當考慮到定點運算時,情況有所不同。新一代GPU在浮點速率相同的情況下可執行整數運算,例如:當Virtex-6設備提高至500GOPS時,GPU每秒可執行1012次運算或1TOPS。整數性能是TILE處理器的優勢所在:8位數據時,TILE-Gx(圖1)最高執行能力為750GOPS,32位數據時為188GOPS。

FPGA能夠利用其并行及適應多種算法的特性來獲得更加接近理論最大值的性能。但是,FPGA需要更大的硅片空間和更長的開發時間來接近這些理論最大值。對于適應于GPU硬件并行模式的算法,GPU已經能夠達到峰值的20~30%。它們同樣具有合理的硅密度(40nm工藝,32nm研發中)和開發時間(通常只有數周,而FPGA則需幾個月)。TILEPro64處理器可提供FPGA相類似的適應性和GPU相類似的可編程性,但是,由于其粗糙的任務級問題分解特點使得其無法像FPGA和GPU那樣實現細粒度并行。

相關推薦

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

-

herbertwj | 2004-08-15

-

-

-

-

-

-

-

xiaohua | 2002-09-24

-

sandman555 | 2005-02-05

-

評論