基于DSP+FPGA的數字導彈飛控計算機設計

摘要:針對在舵機、導引頭、慣導等彈上設備日益數字化的趨勢下飛控系統的需求,提出了一種基于DSP+FPGA結構的通用飛控計算機平臺。DSP+FPGA結構能發揮兩種處理芯片各自的優勢,而且具有良好的通用性和擴展性。針對多個外部設備數據同步問題,采用2個雙端口RAM交替工作的方法,保證各彈上設備數據幀的同步和完整連續。通過半實物仿真系統的驗證,飛控計算機性能良好,性能滿足設計要求。

本文引用地址:http://www.j9360.com/article/201610/309283.htm關鍵詞:DSP+FPGA;數字式飛控計算機;雙端口RAM;數據同步

飛控計算機是現代導彈制導與控制系統的核心裝置,其性能的好壞直接關系到精確制導的精度和殺傷目標的概率。近年來舵機、導引頭、慣導等彈載設備日益向著數字化方向發展,因此設計一種能兼容多數字式設備的通用飛控計算機平臺尤為重要。傳統的單處理器核心飛控計算機難以在多通道異步數據收發的同時保證數據處理速度,難以滿足現代導彈的要求。本文提出了一種基于DSP+FPGA結構,對外接口為422的通用數字飛控計算機平臺。此平臺能充分發揮DSP的運算速度,實現飛控算法。采用基于FPGA的雙RAM緩沖機制,能很好地解決異步串行數據實時同步數據處理問題,滿足飛控系統需求。

1 設計思想和工作原理

1.1 設計思想

對于單DSP核心的飛控計算機,要收發多路異步串行數據就會占用多路中斷,導致中斷響應不及時造成數據丟失。同時多路中斷也會影響到數據傳輸的實時性。飛控計算機對數據的完整性和實時性要求較高,傳統單DSP核心不能滿足彈上多數字式設備的要求。由于FPGA具有強大的并行處理能力,所以采用增加一片FPGA用于異步串行數據的收發的方法彌補單DSP核心的缺陷。DSP+FPGA的結構能將DSP從繁瑣的外部接口管理中解放出來,充分發揮DSP的運算優勢,提高運算效率的同時易于維護和擴展。

1.2 飛控計算機工作原理

飛控計算機的一般工作過程如下:飛控計算機上電之后進行自檢,向載機發出“導彈存在”指令。飛控計算機接收載機的裝訂信息,完成初始對準,并且向載機發出“允許發射”指令。當導引頭探測到目標向飛控計算機發出導引數據時,飛控計算機向載機發出“目標截獲”指令。載機經過判斷決策,向飛控計算機給出“發射”指令。發射之后,飛控計算機進行飛行時間計時,并開始按照已有的控制率,結合慣導和導引頭輸入進行飛控解算,得出四路舵機控制信號信號,控制導彈運動;并將接收到慣導數據、導引頭數據、舵控量等內容組成遙測信息,發送給觀測人員。

2 結構和硬件設計

根據飛控計算機工作原理,它具備以下功能:

能夠收發裝訂、慣導、導引頭和遙測等數據;

能夠實現導引率,完成導航數據解算功能;

能夠控制執行機構——舵機。

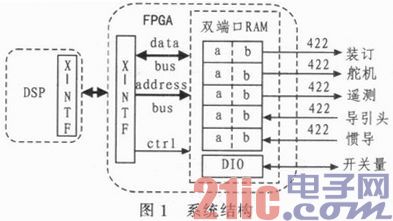

RS422通信協議具有抗干擾能力強,傳輸距離遠,實現簡單的特點,已經被各種數字設備廣泛采用。本彈載機對外通信接口均采用422通信協議。根據飛控計算機的功能可以得出,此系統至少應該包含裝訂、慣導、導引頭、遙測數據的收發和舵機控制5路數據通信。由于彈載機工作時收發“導彈存在”、“目標截獲”、“允許發射”等開關量,還需要開關量的輸入輸出。故FPGA對外的接口共包括5路RS422和8位DIO通信接口。系統結構簡圖如圖1所示(圖中XINTF接口和雙端口RAM的說明見本文第4部分)。

DSP選用TI公司的高性能浮點處理器TMS320F28335,150 MHz主頻,性能相比于2812有大幅提升,廣泛應用于控制系統。FPGA選用ALTERA的Cyclone II系列,完全滿足應用需求。DSP+FPGA組成的最小系統主要由電源、復位電路、晶振、燒寫接口等部分組成。電源芯片選用TPS7 67D301PWP,可以為DSP提供3.3 V的工作電壓和1.9 V的內核電壓;FPGA的內核電壓由ASM1117-1.2穩壓得到。DSP復位芯片采用MAX809S,晶振采用30 MHz的有源晶振;FPGA用50 MHz的有源晶振。配置芯片選用EPCS1,容量為1M bits,用AS模式燒寫。

對外的RS422接口采用MAX3491協議芯片實現。MAX3491將FPGA的TTL電平轉換成422差分電平,和彈上設備通信。由于FPGA引腳的驅動能力弱,因此對外的8位DIO采用74LN244芯片,增強驅動能力。

3 軟件設計

DSP通過XINTF接口與FPGA通信。DSP將地址傳遞給FPGA,FPGA經過地址譯碼操作對應外部設備數據。

3.1 FPGA軟件設計

FPGA主要功能是完成5路RS422串口數據的同時收發操作開關量的輸入和輸出,并和DSP交換數據。FPGA可使用進程語句實現并行運行,對各外設的操作都是實時并行的,相互之間沒有影響。

3.1.1 串口通信

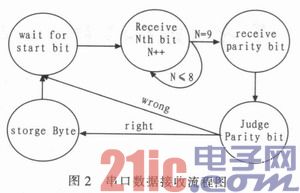

先將時鐘通過分頻得到8倍于波特率的串口時鐘。數據接收時,根據串口通信的特點,首先判斷低電平起始位。檢測到起始位之后,按照嚴格地每八個時鐘一位的關系采集一個字節8位的電平。由于噪聲的存在可能會導致采集到的瞬時電平有誤,此時采用表決機制,即在8個時鐘期間采樣3次,以其中2次相同的電平為準。實驗證明,表決機制能極大排除隨即噪聲干擾,降低串行通信的誤碼率。接收到數據之后存儲在對應的雙端口RAM中,等待DSP讀取。串口數據接受流程如圖2所示。

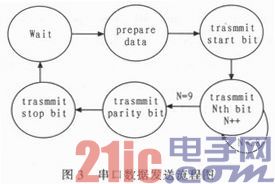

數據發送時先從雙端口RAM中讀出需要發送的數據,按照串口時鐘,先發送起始位(低電平),再依次通過移位寄存器將8位的數據轉換成串行的‘0’/‘1’發出。主要由下面語句實現:

txd=txd_buf(0);

txd_buf(6 downto 0)=txd_buf(7 downto 1);

其中txd是要發送的1位邏輯電平,txd_buf中存儲著將要發送的數據。發送流程如圖3所示。

將按照上述流程設計的程序在FPGA中進行測試。將FPGA串口和PC機連接,采用115 200波特率連續工作3分鐘,收發均無錯誤字節。

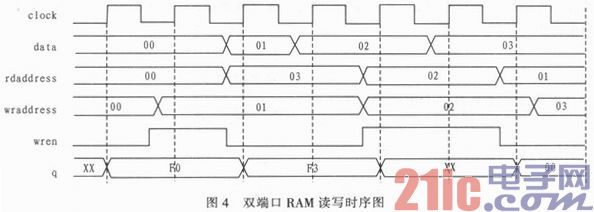

3.1.2 雙RAM緩沖機制

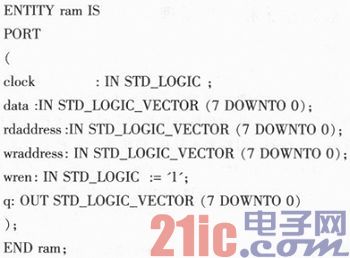

由于串口外設的波特率是115 200,屬于低速外設,因此在串口數據和DSP之間采用雙端口RAM作為緩沖區。由于此FPGA上自帶片上RAM,因此可以利用開發環境自帶的IP核生成片上雙端口RAM,不用額外增加片外RAM器件(圖1)。雙端口RAM的實體定義和讀寫時序:

將每個RAM中的最后一個字節作為反映RAM存儲狀態的狀態字。RAM的狀態字代表的含義如下:

bit0:1-串口接收到新數據幀 0-無新數據幀;

bit1:1-數據已經被讀取 0-數據未被讀取;

慣導和導引頭向彈載機每6 ms傳輸一幀數據,將數據存儲到雙端口RAM中,同時將bit0置‘1’,bit1清零,即RAM狀態為“新數據幀未被讀取”。由于慣導和導引頭的數據不同步,因此DSP每1ms就查詢一次RAM的狀態字。若接收到新的數據幀(bit0=1),則讀取RAM數據,并將“數據被讀取”位置1(bit1=1)。這樣,慣導和導引頭給DSP發送的數據延遲不超過1 ms,可以認為慣導和導引頭的數據是實時同步的。

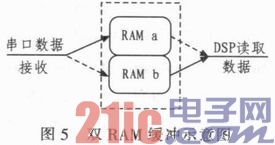

在串口接收數據期間,如果串口和DSP在同一時間操作RAM,可能導致DSP讀取到幀錯亂的數據。為了保證數據幀的完整,不使兩者同時讀取RAM,采用雙RAM緩沖機制,即為每個串口配置2個雙端口RAM的作為緩沖,如圖5所示。串口數據接收程序通過查詢RAMa和RAMb的狀態字,若bit1=1,則將接收到的數據幀存儲到對應的RAM中,完成之后將bit0置1,bit1清0,這個周期為6 ms。與此同時,DSP每1 ms查詢一次RAMa和RAMb,若bit0為1,則讀取對應RAM中的數據幀,同時將bit0清0。bit1置1。串口數據發送過程與接收類似,數據傳輸方向相反。

采用雙RAM緩沖機制,使得串口和DSP不在同一時間訪問同一RAM區,避免了錯幀和丟幀,同時保證了數據傳輸的實時性。

3.2 DSP軟件設計

DSP軟件設計采用模塊化設計方式,分為應用層和底層軟件兩部分。應用層軟件主要實現飛控流程和飛控算法;底層軟件主要實現數據格式的轉換,以便通過DSP總線和FPGA進行數據交換。

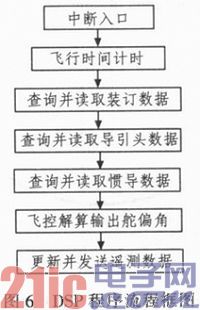

3.2.1 應用層軟件設計

外部的慣導和導引頭6 ms產生一次數據,DSP開啟1ms的定時器中斷,在中斷中每1 ms查詢一次雙端口RAM的狀態字,判斷是否有新數據產生,這樣采集的數據延遲不會超過1 ms。飛控解算的周期為6 ms,遙測數據發送的周期為12 ms,在定時器中斷程序中完成飛控解算和遙測數據發送。

中斷服務程序每1 ms運行一次,每次首先查詢導引頭和慣導有沒有更新數據,再讀取新數據存儲在全局結構體里。每6ms用全局結構體里得到的新數據解算一次飛控指令,得到舵機的輸出角度,輸出舵控指令,控制舵機。流程如圖6所示。

3.2.2 底層軟件設計

DSP底層軟件主要完成外部數據交換和數據格式的轉換。DSP通過XINTF產生讀寫時序(圖2圖3所示時序),FPGA也設計與之相匹配的時序完成兩者之間的數據交換。

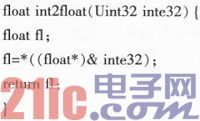

DSP應用層軟件使用的是浮點數,而DSP和FPGA之間只能傳遞二進制數,因此需要按照IEEE標準進行浮點數和二進制數之間的轉換。根據IEEE標準,可以用32位,即8個字節表示一個浮點數。如果將代表浮點數的4個字節組合成32位的整型數inte32,進行強制類型轉換皆可以得到浮點數,轉換函數如下:

將浮點數轉換成整型數的方法與此類似。底層軟件按照上述方法實現數據轉換,供應用層調用。

4 系統驗證

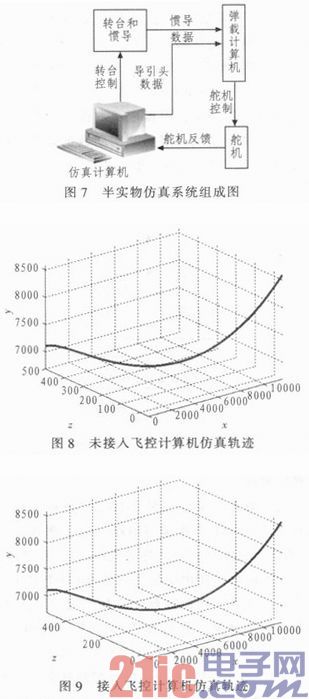

彈載機實物設汁制作完成之后可以利用半實物仿真平臺進行測試,該半實物仿真平臺由上位機、慣導、舵機和三軸轉臺組成。如圖上位機的作用是模擬導彈動力學模型和導引頭信息,并控制三軸轉臺運動模擬導彈姿態。導彈的運動信息由慣導測量之后發送給飛控計算機,飛控計算機根據運動信息解算出舵機控制量控制舵機轉動,同時將遙測數據發送給上位機。上位機采集舵機反饋的實際角度,將其代入導彈動力學模型,計算導彈姿態,控制三軸轉臺,這樣就形成了完整的半實物仿真回路。

仿真實驗中,首先不接入飛控計算機,由仿真計算機中的控制系統數學模型直接實現控制算法,所得導彈運動軌跡如圖8所示;將飛控計算機接入仿真回路,由飛控計算機實現制導控制算法所得運動軌跡如圖9所示。

由圖8和圖9的對比可以看出,飛控計算機接入之后飛控系統工作正常,導彈飛行軌跡基本一致,飛控計算機控制效果理想。

5 結論

文中提出了一種基于DSP+FPGA的飛控計算機設計方法,在半實物仿真系統中驗證了其性能,滿足設計要求。解決了在多數字彈上設備存在情況下的數據幀實時同步問題。由于FPGA可以通過編程實現各種時序,所以此飛控計算機可以擴展為除了RS422外部接口外的其他多種數字設備接口,滿足模塊化、通用化的實際應用需求。

評論