一種高性能時鐘晶體振蕩器電路設計

摘要 設計了一種用于時鐘芯片的Pierce晶體振蕩器,通過對傳統結構的改進,增加了振幅控制結構和輸出頻率校準電路,提高了輸出頻率、振幅的穩定性和輸出頻率的精度,降低了功耗。同時對電路的工作原理進行了理論分析,電路采用CSMC 0.5μm-5 V CMOS工藝實現,通過仿真結果驗證,顯示該設計達到了技術指標要求。

本文引用地址:http://www.j9360.com/article/201610/309282.htm晶體振蕩器具有穩定的諧振特性和較高的品質因數Q,因此其諧振特性既精確又穩定,被廣泛應用于彩電、計算機、遙控器等各類振蕩電路中,以及通信系統中用于頻率發生器、為數據處理設備產生時鐘信號和為特定系統提供基準信號。目前所用的時鐘芯片大都采用32.768 kHz晶振,為系統提供穩定的32.768 kHz初始振蕩頻率。但晶體振蕩屬于機械諧振,其需要合理的設計諧振電路與晶體配合。Pierce晶體振蕩器其結構簡單,便于集成,故得到了廣泛應用。小型化、低功耗、高精度始終是此類芯片的發展研究方向。但傳統的Pierce電路結構存在輸出振幅受電源電壓變化影響、功耗偏大、且輸出頻率受寄生效應影響等缺點。針對上述不足,本文設計了改進方案:(1)增加振幅控制電路,降低振蕩輸出波形的幅度,提高振幅的穩定性,同時降低電路的功耗。(2)增加頻率校正電路,可使芯片的輸出頻率得到精確校準,消除晶振固有參數變化和芯片封裝管腳的寄生電容對輸出頻率的影響,在具有溫度檢測功能的系統中還可實現輸出頻率的溫度補償,最終實現振蕩電路的低功耗與高精度的頻率輸出。且采用該設計還可獲得高性能的時鐘日歷芯片。

1 晶振與Pierce晶體振蕩器

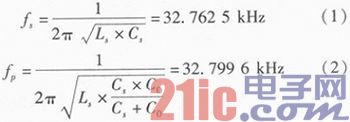

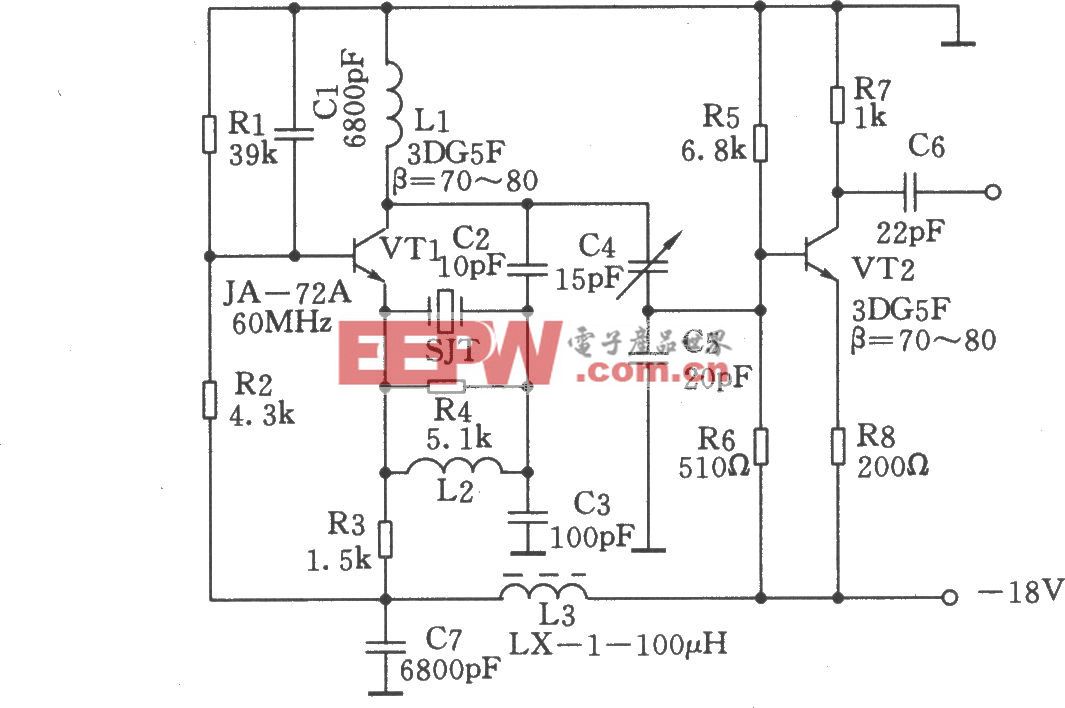

晶片振蕩是基于其壓電效應,其等效電路圖如圖1中所示。石英晶體的等效電路由靜態電容CO,串聯等效電感LS、串聯等效電容CS、串聯損耗電阻RS組成。從石英晶體的等效電路可知,其有兩個諧振頻率,一個串聯諧振頻率fS,一個并聯諧振頻率fP,只有在頻率fS真和fP之間石英晶體成感性,為晶體的振蕩帶。本文仿真選取32.768kHz石英晶體等效模型參數為:CO=1.3pF,LS=8kH,CS=2.95 fF,RS=30kΩ,可計算得到

該模型的振蕩帶寬為fP-fS=37.1 Hz,精度滿足仿真要求。

圖1中Pierce電路是該電路的典型結構。電路以反相放大器作為增益元件,在反相器的輸入與輸出之間跨接一個負反饋電阻RF,該電阻一方面給反相器提供直流偏置,穩定反向放大器的靜態工作點;另一方面,起振之后構成負反饋,減小反相放大器的增益,穩定振幅。其電阻阻值必須足夠大從而增加頻率的穩定性和降低振蕩電路的功耗。圖中RF約為100 MΩ,為減小芯片的面積,設計采用MOS管實現。C1與C2構成品振的負載電容,Q為石英晶體。

2 改進后的Pierce振蕩器

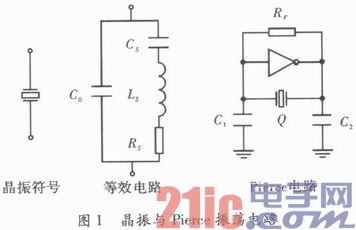

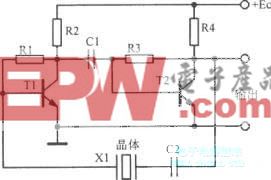

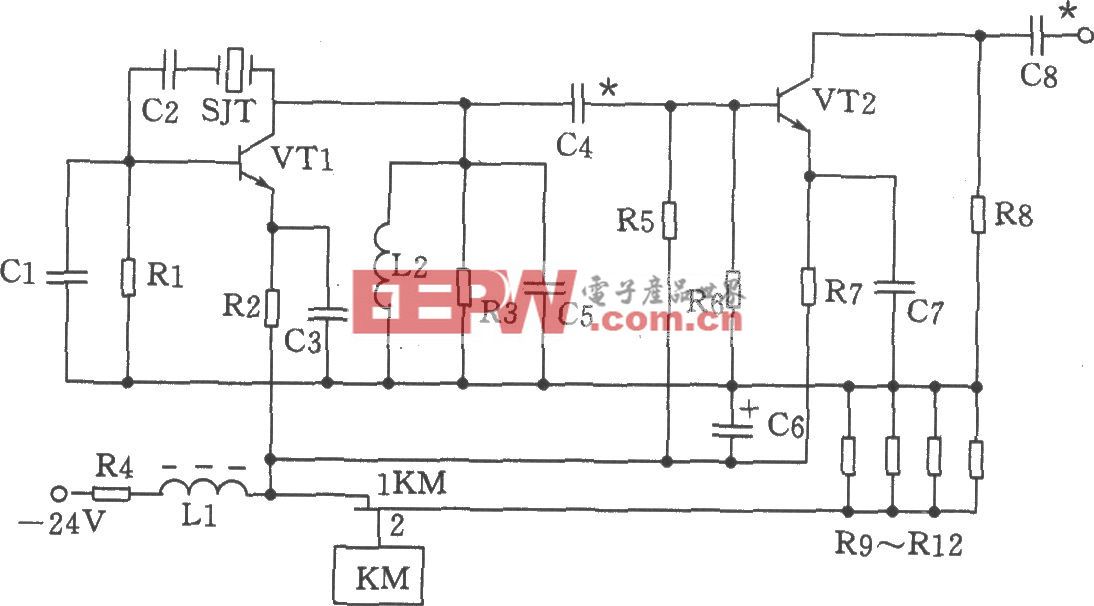

傳統的Pierce振蕩器結構簡單,輸出波形振幅大,導致振蕩電路功耗較大,輸出頻率也受石英晶體的出廠頻率以及芯片PAD電容和PCB上布線寄生電容等的影響,芯片工作時實際輸出頻率與理想頻率(32.768 kHz)之間存在一定的頻率偏差,因此在對功耗和頻率精度要求嚴格的時鐘芯片設計應用中受到限制。針對以上不足,本文對傳統的Pierce結構進行了改進:(1)增加振幅控制電路;(2)增加頻率校準電路。改進后的電路結構由頻率校準模塊、反相放大模塊、振幅控制模塊、啟動電路模塊4部分組成,其設計電路如圖2所示。

2.1 頻率校準的原理與電路設計

晶體振蕩電路的實際輸出頻率與晶體的固有串聯諧振頻率之間存在一定的頻率牽引量,為

,其中,ω是實際輸出頻率;ωs是晶振的固有串聯諧振頻率。

頻率牽引量與負載電容關系如式(3)所示

式(3)中,C0是晶振的靜態電容;Cs是晶振的固有串聯諧振電容;C1、C2是晶振兩端的電容,其串聯值稱為晶振的負載電容。當出廠頻率與理想頻率之間存在一定偏離時,可通過校正晶振的負載電容,得到精確的輸出頻率。

頻率校準實現電路如圖2中頻率校準部分。T7~T0為內部8位校正寄存器的存儲值,通過I2C接口寫入。當輸入信號T6~T0是高電平時,控制相應的NMOS管導通,使晶振負載電容增大。而當T7是高電平時,NMOS15、NMOS19截止,使負載電容減小,所以B7為負載電容調整的符號位。當芯片通電時,上電復位信號使校正寄存器復位,T7~T0輸出均為0,因此晶振兩端的電容初始值為CX+27C,其變化范圍分別為[CX,CX+(28-1)C]。

2.2 振幅控制原理與電路設計

若振蕩器的輸出振幅較大,不僅顯著增大了振蕩電路的功耗,還會降低晶振的壽命。振幅控制電路的設計原理是:電路檢測振蕩輸出的振幅,反饋確定反向放大器的偏置電流,振蕩輸出振幅大于設定值時,振幅控制電路降低反向放大器的偏置電流,反之,增大反向放大器的偏置電流。電路在上電時,振蕩輸出振幅為0,使反向放大器具有大的偏置電流,有利于起振。其電路如圖2中振幅控制模塊所示。M1、M2、M4、M5和R1構成與電源電壓無關的偏置電流源,M1和M2的寬長比比值為1:2,M4,M5的寬長比的比值為1:8。為降低功耗,設計使偏置電流源中的MOS管工作在亞閾值區,設流過M1管的電流為2I,可得到

其中,ID4、ID5分別為流過M4,M5的電流,N為亞閾值斜率參數。將VGS4-VGS5=4I×R1,代入等式(4)中可得

,該偏置電流與電源無關,通過選取適當的R1值,便可設置所需的偏置電流。設計取電流I≈8 nA,確保電路具有較低的功耗。

圖2中電阻R2跨接在M4柵漏兩端,MOS管的柵端無電流,因此M4柵漏間的直流電壓相等。若漏電流保持不變,M4柵極上的平均電壓應保持不變。當振蕩器開始工作后,振蕩輸出的信號經電容C0隔直通交后,傳遞M4的柵極。當振幅增大時,若要保持恒定的偏置電流不變,M4柵極直流電壓必定下降,因此M5的柵極電壓也必定隨著振幅增大而下降,從而使偏置電流I減小。反向放大器的偏置電流由電流源M3確定,大小為16I,因而當振蕩器的輸出振幅振蕩增大時,系統降低反向放大器的偏置電流,以到達穩定振幅、減小功耗的目的。

2.3 反向放大電路模塊與啟動電路模塊的設計

改進后的電路結構還包含反向放大電路模塊和啟動電路模塊。反相放大電路采用恒流偏置共源放大器,由M3提供恒流偏置,M6為共源放大管,R3為負反饋電阻。恒流偏置電流的大小為16I,受振幅控制電路調制。

啟動電路模塊,保證電路上電后能正常啟動。在直流偏置未建立時,M9輸出電流為0,M10導通使反相器I1輸出低電平,PMOS管M11導通,給電容C3充電,使B點電壓升高,從而M2,M5導通,保證偏置電流可正常建立。當直流偏置建立后,M9通過鏡像產生10I的電流,M10管的柵長值L過大,使反向器I1輸出變為高電平,關斷M11,電路完成啟動。

3 電路仿真結果及討論

3.1 晶體振蕩電路環路增益與相位仿真

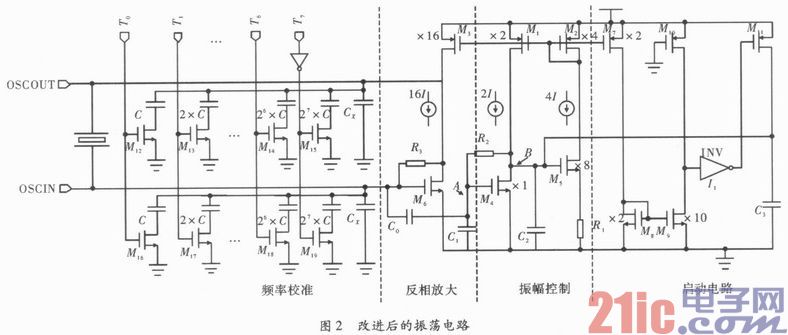

仿真采用0.5μm-5 V CMOS工藝模型,仿真溫度設定25℃,仿真工具是Spectre。圖3是設計的晶體振蕩電路環路增益與相位仿真結果,電源電壓分別設定為3 V和1.1 V,晶體負載電容為6 pF的條件下,從仿真圖中可看出,在頻率為32.768 1 kHz處,環路增益為5.285 5,相位為0,在該頻率處滿足振蕩的條件。當電壓下降到1.1 V時,同樣在頻率為32.7681kHz處,環路增益為3.833 0,相位為0,也滿足振蕩條件。這表明其可在1.1V電壓下正常振蕩,電路具有較寬的工作電壓范圍。

3.2 晶體振蕩電路瞬態仿真

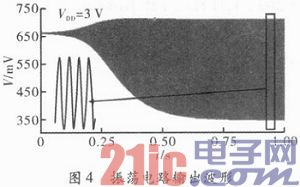

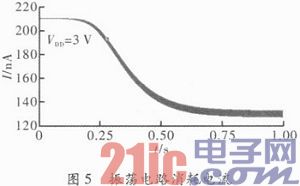

圖4和圖5均為電源電壓為3 V時,振蕩電路的瞬態仿真結果,其分別反映了振蕩電路的輸出波形以及電路消耗的電流。從圖中可看出,振幅控制的過程:在起振初期振幅較小時,電路消耗較大的電流,隨著振幅的增大,振幅控制電路調控偏置電流,使電路消耗的電流降低。當電路穩定后,電流最終消耗值約為130 nA,振蕩電路輸出波形峰峰值為367.2 mV。電路消耗極低的功耗,且起振時間1 s。

3.3 頻率校準仿真

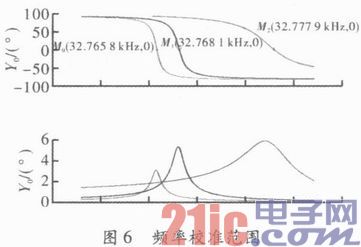

圖6為頻率校準范圍的仿真圖,設計取Cx=4.4 pF,C=62fF。調整校正寄存器的存儲值,使晶體振蕩器的負載電容分別為最大值、初始值和最小值。仿真得到滿足起振條件的初始頻率為32.768 1 kHz,頻率校準范圍為(32.765 8 kHz,32.777 9 kHz),校準的平均精度為1.44ppm。通過校準電路可獲得高精度的輸出頻率。

4 結束語

高精度使得時鐘芯片的市場前景廣闊。本文對傳統Pierce振蕩器結構進行了改進,反向放大器采用恒流源供電,增加振幅控制及頻率校準電路。仿真結果表明,新結構的電路具有低功耗、高輸出頻率精度和寬工作電壓范圍等優點。

評論