京微雅格重磅之作―新版FPGA/CAP設(shè)計套件Primace5.0

簡介

本文引用地址:http://www.j9360.com/article/201610/308581.htm作為國內(nèi)唯一一家具有完全自主知識產(chǎn)權(quán)的FPGA與可配置應(yīng)用平臺CAP(Configurable Application Platform)產(chǎn)品供應(yīng)商,京微雅格一直在快節(jié)奏的改進(jìn)與產(chǎn)品配套的軟件開發(fā)環(huán)境。最近,新一代FPGA/CAP設(shè)計套件Primace5.0正式發(fā)布了。Primace5.0完整的支持了基于時序驅(qū)動的布局布線實(shí)現(xiàn)流程(Timing-Driven PlacementRouting Flow),提高了布局布線的成功率,減少了設(shè)計與驗(yàn)證時間。此外,Primace5.0還配套改進(jìn)了Synopsys SDC兼容的設(shè)計約束輸入界面, 方便用戶更加準(zhǔn)確高效的輸入時序約束。配合新型的自動尋找最佳實(shí)現(xiàn)的優(yōu)化工具iXplorer,Primace 5.0可以極大的加速用戶設(shè)計時序收斂過程。為了方便用戶準(zhǔn)確描述設(shè)計,改善RTL 代碼質(zhì)量,Primace5.0新增了RTL Template功能,其中包括了常用的Verilog設(shè)計元素。Primace5.0還第一次完整支持了8051MCU的SoC仿真以及時序仿真(Timing Simulation)。相對上一代版本,新一代Primace顯著改進(jìn)了用戶信息提示以及流程的穩(wěn)定性。本文將簡要介紹這些改進(jìn)以及對用戶使用體驗(yàn)的影響,并推薦幾種可以有效改進(jìn)設(shè)計流程,加速設(shè)計過程的方法。

Primace5.0主要新增/改善的功能

Primace5.0中基本設(shè)計流程保持了一貫的簡潔的特點(diǎn),如圖1所示,主要包括設(shè)計輸入(RTL編輯等),設(shè)計實(shí)現(xiàn)(綜合、布局布線等),時序收斂(以靜態(tài)時序分析為基礎(chǔ)的設(shè)計、實(shí)現(xiàn)調(diào)整),以及碼流下載和片上調(diào)試(DebugWare等)。

圖1: Primace中FPGA/CAP開發(fā)流程

基于時序驅(qū)動的布局布線

時序驅(qū)動的布局布線是一種已經(jīng)被廣泛證明與接受的設(shè)計方法,設(shè)計人員通過描述設(shè)計的時序約束(包括核心頻率約束,I/O約束,例外約束,特定路徑約束,跨時鐘域約束等)可以有效指導(dǎo)布局布線程序高效、高質(zhì)量的完成設(shè)計實(shí)現(xiàn)。Primace5.0中接受的時序約束包括:

Basic Timing Path

Clock Setup/Hold, Falling edge

Tsu/Th, Tco, Tpd

Advanced Timing Path

False path

Generated clock

User edited sdc

時序約束輸入輔助

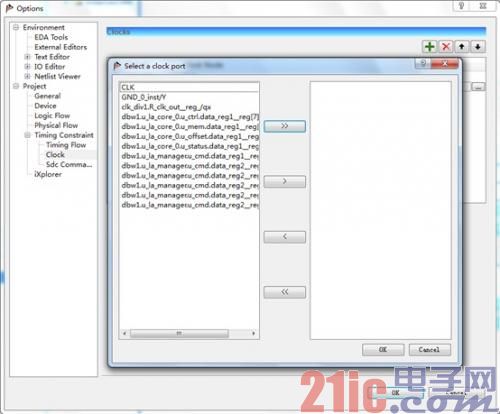

為了方便用戶可以準(zhǔn)確高效的輸入時序約束,Primace5.0還配套改進(jìn)了兼容Synopsys SDC的設(shè)計約束輸入界面。如下圖所示:

圖2: 選擇時鐘界面

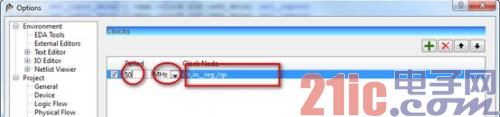

圖3:時鐘約束設(shè)置界面

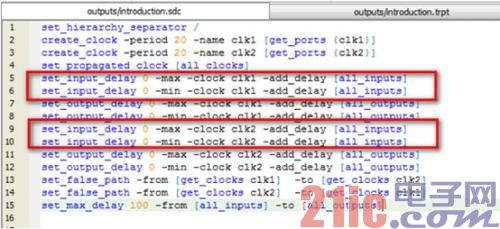

各類SDC最終匯總在統(tǒng)一的SDC約束文件里,用戶可以集中編輯:

圖4:SDC編輯界面

時序收斂工具iXplorer

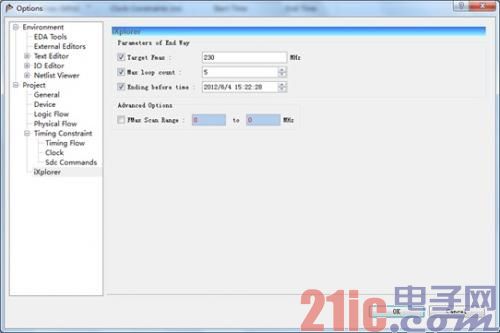

配合新型的自動尋找最佳實(shí)現(xiàn)的優(yōu)化工具iXplorer,用戶可以極大的加速設(shè)計時序收斂過程。

圖5:iXplorer配置界面

Primace5.0對iXplorer進(jìn)行了多項(xiàng)重要改進(jìn)。首先,引入了支持并行執(zhí)行流程的新一代流程控制引擎,充分的利用了主流多核系統(tǒng)的計算資源。其次,新開發(fā)的新型fMAX掃描算法Range-Scan,在充分利用了并行計算優(yōu)勢的基礎(chǔ)上,可以智能掃描時序約束(目前主要是時鐘頻率約束),用最短的時間尋找不同時序約束下設(shè)計實(shí)現(xiàn)的最佳fMAX。此外,iXplorer支持多種掃描結(jié)束條件,方便用戶在多種需求下的靈活使用。最后,當(dāng)用戶得到最佳fMAX結(jié)果后,iXplorer提供了便捷的方式讓用戶把相應(yīng)的約束條件設(shè)置到用戶環(huán)境,從而可以得到相應(yīng)的結(jié)果。

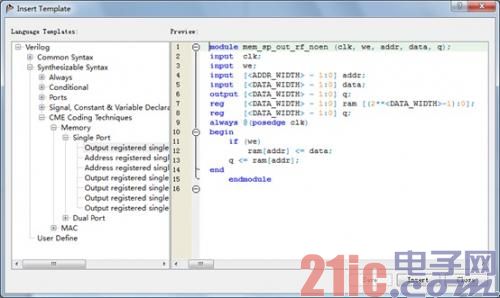

RTL模板

為了方便用戶準(zhǔn)確描述設(shè)計,改善RTL 代碼質(zhì)量,Primace5.0新增了RTL Template功能,其中包括了常用的Verilog設(shè)計元素。通過使用RTL Template,用戶可以方便快捷的在設(shè)計中插入經(jīng)過Primace軟件驗(yàn)證的RTL代碼,簡化了用戶設(shè)計輸入過程并提高了設(shè)計代碼質(zhì)量。目前Primace RTL Template主要支持了以下幾類設(shè)計元素:

通用語法(注釋,編譯器控制語法等)

可綜合語法(目前僅支持Verilog可綜合子集,以及Memory, Multiplier等可以自動推斷的代碼模式)

用戶自定義模板

圖6:RTL模板瀏覽界面

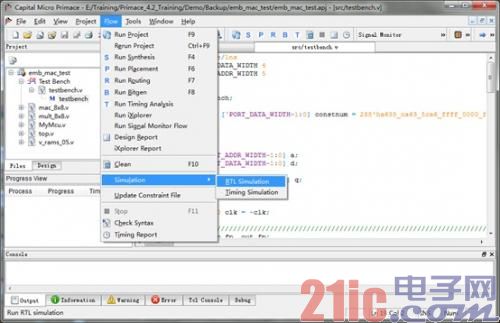

SoC仿真與時序仿真

Primace5.0還第一次完整支持了8051MCU的SoC仿真,以及時序仿真(Timing Simulation)。首先,通過簡明易用的工程文件管理,方便用戶對設(shè)計文件和測試平臺文件進(jìn)行編輯和管理;其次,引入了對8051MCU的SoC仿真支持,完全改變了過去調(diào)試8051MCU需要依賴第三方工具的調(diào)試模式,大大提升了用戶SoC設(shè)計的調(diào)試效率,加快了用戶SoC設(shè)計的整個驗(yàn)證和調(diào)試流程。最后,引入了對時序仿真的支持,為解決用戶設(shè)計中遇到的時序收斂問題提供了一條全新的分析和調(diào)試的途徑,加快了用戶設(shè)計時序收斂的過程。

圖7:仿真調(diào)用界面

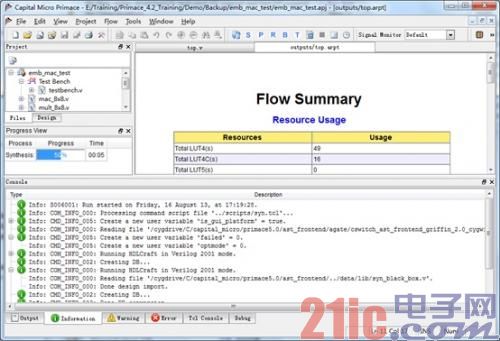

流程及信息提示

相對上一代版本,新一代Primace顯著改進(jìn)了用戶信息提示以及流程的穩(wěn)定性。Primace 5.0對用戶設(shè)計實(shí)現(xiàn)中各個階段的流程信息重新進(jìn)行了劃分,將所有信息分為4類:命令信息,執(zhí)行信息,警告信息和錯誤信息,對每一類信息逐條進(jìn)行了編號,并引入了同類信息的折疊顯示,方便用戶通過流程信息了解設(shè)計實(shí)現(xiàn)的實(shí)時情況。此外,良好的用戶信息分類和顯示也提升了流程日志的可用性,進(jìn)一步方便用戶了解設(shè)計實(shí)現(xiàn)的過程。

圖8:信息提示界面

使用技巧

時序約束設(shè)置方法

時序約束設(shè)置基本可以遵循先整體后局部,先高層后低層的規(guī)律分階段、分步驟的逐步細(xì)化設(shè)置。用戶可以按照以下順序設(shè)置時序約束:

核心頻率約束

通過約束每個時鐘的時鐘頻率以及相位關(guān)系,可以完成基礎(chǔ)的核心頻率約束。目前Priamce5.0支持的這類約束包括Clock Setup,Clock Hold,F(xiàn)alling edge, Generated Clock。

I/O約束

I/O約束包括引腳分配位置、空閑引腳驅(qū)動方式、外部走線延時(InputDelay、OutputDelay)、上下拉電阻、驅(qū)動電流強(qiáng)度等。加入I/O約束后的時序約束,才是完整的時序約束。FPGA作為PCB上的一個器件,是整個PCB系統(tǒng)時序收斂的一部分。FPGA作為PCB設(shè)計的一部分,是需要PCB設(shè)計工程師像對待所有COTS器件一樣,閱讀并分析其I/O Timing Diagram的。FPGA不同于COTS器件之處在于,其I/O Timing是可以在設(shè)計后期在一定范圍內(nèi)調(diào)整的;雖然如此,最好還是在PCB設(shè)計前期給與充分的考慮并歸入設(shè)計文檔。正因?yàn)镕PGA的I/O Timing會在設(shè)計期間發(fā)生變化,所以準(zhǔn)確地對其進(jìn)行約束是保證設(shè)計穩(wěn)定可控的重要因素。許多在FPGA重新編譯后,F(xiàn)PGA對外部器件的操作出現(xiàn)不穩(wěn)定的問題都有可能是由此引起的。目前Primace5.0支持的這類約束包括Tsu,Th,Tco,Tpd。

時序例外約束

時序例外約束可以指出在全局約束下的特殊路徑集合,使得最終的時序約束準(zhǔn)確,嚴(yán)格。正確的應(yīng)用例外約束可以提高時序分析報告質(zhì)量,加快時序收斂過程。目前Primace5.0通過FalsePath來支持時序例外約束。

“好的時序是設(shè)計出來的,不是約束出來的”,好的約束必須以好的設(shè)計為前提。沒有好的設(shè)計,在約束上下再大的功夫也是沒有意義的。不過,通過正確的約束也可以檢查設(shè)計的優(yōu)劣,通過時序分析報告可以檢查出設(shè)計上時序考慮不周的地方,從而加以修改。通過幾次“分析-修改-分析”的迭代也可以達(dá)到完善設(shè)計的目標(biāo)。應(yīng)該說,設(shè)計是約束的根本,約束是設(shè)計的保證,二者是相輔相成的關(guān)系。

基于iXplorer的時序收斂方法

時序收斂(Timing Closure)指時序的不斷逼近,原理是采用多次迭代(循環(huán))的技術(shù)。因此時序收斂就是一個不斷反復(fù)的過程,以確保設(shè)計中的每個路徑都滿足時序要求。iXplorer是京微雅格定義的,嵌入在Primace工具中的時序收斂設(shè)計流程。Primace有很多選項(xiàng)設(shè)置和策略,但是無法保證哪種選項(xiàng)或約束會對所有的設(shè)計帶來最佳的效果。iXplorer技術(shù)能夠幫助用戶找到最佳的工具選項(xiàng)來實(shí)現(xiàn)時序要求或者找到設(shè)計的最高性能。iXplorer通過采用不同策略和選項(xiàng)來運(yùn)行多個布局布線版本并找出滿足時序要求的實(shí)現(xiàn)結(jié)果。目前iXplorer支持三種搜索算法來滿足不同場景下的使用需求:

Target fMAX,用戶指定期望的fMAX,啟動iXplorer后,iXplorer開始嘗試不同約束與選項(xiàng),直到達(dá)到給定的fMAX停止。

Max Loop Count,用戶指定最多iXplorer嘗試不同約束與選項(xiàng)組合的次數(shù),從給定次數(shù)的運(yùn)行結(jié)果中找到最佳實(shí)現(xiàn)結(jié)果。

Ending Before Time,用戶給定最晚結(jié)束時間,iXplorer會盡可能多的搜索約束與選項(xiàng)的組合,并在給定結(jié)束時間時停止。例如,用戶可以設(shè)結(jié)束時間為第二天早上八點(diǎn),然后在下班前啟動,第二天上班時去查看結(jié)果。

iXplorer會用時序驅(qū)動的技術(shù)根據(jù)頻率目標(biāo)是否達(dá)到來加強(qiáng)或放松時序目標(biāo),這樣就可以判斷出所指定時鐘域的最高頻率限制。在優(yōu)化結(jié)束后,用戶可以從iXplorer報告中看到究竟哪種策略和選項(xiàng)對目前的設(shè)計是最佳的。

總結(jié)

Primace5.0是京微雅格最新發(fā)布的FPGA/CAP設(shè)計套件。本文簡要介紹了Primace5.0包括基于時序驅(qū)動的布局布線等新功能,并針對時序收斂問題給出了兩種基于Primace5.0的設(shè)計方法。限于篇幅,本文不能盡述Primace5.0對用戶設(shè)計體驗(yàn)的改變,如果讀者對Primace5.0有任何問題、意見或建議,請與京微雅格的銷售支持聯(lián)系。

評論