高速數傳中定時同步設計與FPGA實現

摘要 文中對適用于高速突發通信的基于數字濾波平方的定時同步算法進行了研究。通過對在高速數據傳輸通信中,該定時同步環路的定時誤差估計模塊進行并行結構實現,大幅降低了系統對于時鐘的要求,且更加易于實現;將文中所提定時控制部分與其他文獻中的方法做了對比,表明所用方法可以達到更好的效果。最后進行的Matlab仿真以及硬件實現,結果表明,該環路可以實現突發與非突發情況下的高速數傳定時同步。

本文引用地址:http://www.j9360.com/article/201610/308515.htm目前,數字通信系統正向高速全數字化方向發展。在全數字接收機定時同步中,主要包括兩個關鍵點:定時誤差估計和定時控制。傳統的定時同步方法中一般直接調節本地采樣時鐘以達到采樣最佳的效果,而在全數字接收機中,本地采樣時鐘不變,通過計算定時誤差控制產生重采樣時鐘達到最佳采樣。通過產生重采樣時鐘達到定時同步的方法常用的有Gardner算法和數字濾波平方法。二者同屬定時同步中的內插法,對載波信號不敏感,可以先于載波同步進行,差別在于Gardner屬于反饋式,而數字濾波平方法屬于前饋式,所以后者的同步時間更短更適合處理突發信號,因此在存在突發情況的全數字接收機中得到了廣泛應用。數字濾波平方法適用于正在研究項目中,要求可以處理突發情況下MPSK與MQAM調制信號的定時同步,并且在高速通信情況下,通過對算法的定時誤差估計模塊進行并行結構實現,可以大幅降低對于時鐘的要求,所以對數字濾波平方法的研究是必要和有意義的。

1 定時同步原理

對于一般的線性調制信號,有

其中,cn為發送的符號數據;g(t):gT(t)×gR(t)為系統脈沖響應;gT(t)為發送端成型濾波器的脈沖響應;gR(t)為接收端匹配濾波器的脈沖響應;T為符號周期;s(t)為慢變的采樣時間誤差;B(t)為載波相差,這里不考慮載波相差,即B(t)=0,n(t)為高斯噪聲,n(t)~N(0,2δ2),其同相分量和正交分量的方差均為δ2。

對接收信號r(t)以采樣率N/T采樣可得

rk=r(kT/N) (2)

然后對采樣后的信號取模并平方,得xk樣本信號,該樣本信號中包含有一個頻率為1/T的頻譜分量,該頻譜分量中就包含有定時誤差信息。通過計算每一段長為LN(即LN個采樣數據;L代表一次運算的符號數;N表示每個符號的采樣點數;一般取N=4)的數據序列的傅里葉系數提取出來,該系數為

式中求出的定時誤差

為ε的無偏估計。

2 定時誤差估計

2.1 實現框圖

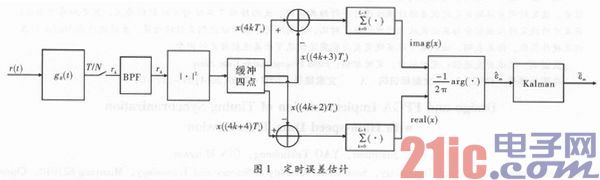

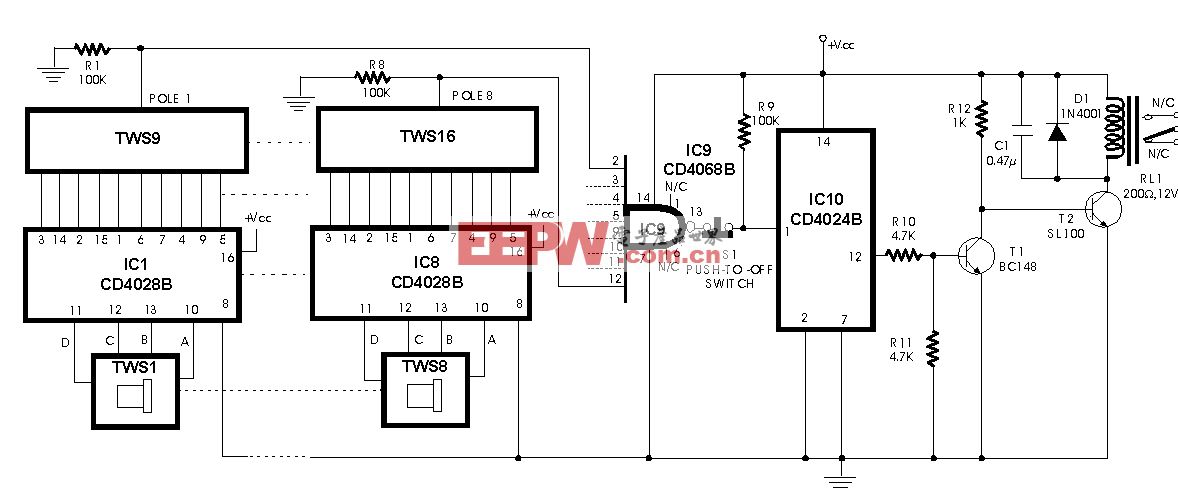

根據式(3),當N=4時通過公式變換可得定時誤差估計實現框圖如圖1所示。

其中,匹配濾波之后,加入一個中心頻率為1/2T,帶寬為α/T的帶通濾波器,用來濾除帶外噪聲,并在誤差求出之后加入一個卡爾曼濾波器,用以對結果進行平滑。

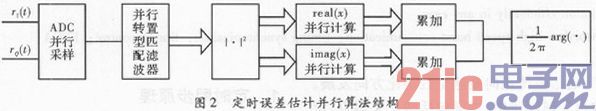

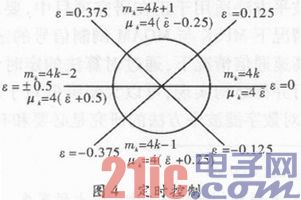

2.2 誤差估計的并行結構

針對高速數據傳輸時的通信,在定時同步的前端,ADC采樣采取并行結構,也即ADC通過并行時間交織的采樣方式進行4倍采樣。然后匹配濾波器設計為并行轉置型FIR,進行并行輸出,輸出的結果再次使用并行結構,分別求出式(5)中image(x)和real(x),并行結構如圖2所示。

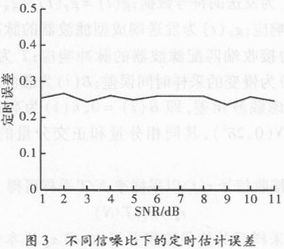

預設定時誤差為1/4,在不同輸入信噪比情況下驗證定時誤差估計的準確性,如圖3所示。定時誤差并行算法結構能夠正確地估計定時誤差。

3 定時控制

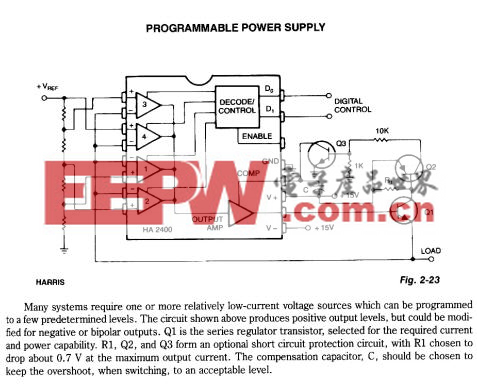

定時控制部分,文獻提到用與Gardner算法中相同的控制方法,即環路濾波和NCO控制。在此,文中使用另外一種定時控制方法,獲得了更好的效果。定時控制部分,文中采用定時估計算法,估計出的誤差值去控制產生內插所要用到的整數間隔mk和分數間隔μk。

Gardner定時控制方法和新控制方法分別為兩種定時控制方法在碼速率為300 MHz,采樣率為1.2 GHz,時偏為0.25T,SNR為15 dB時的星座圖。從星座圖可明顯看出,新控制方法效果更好,星座圖更加收斂。

4 Matlab仿真

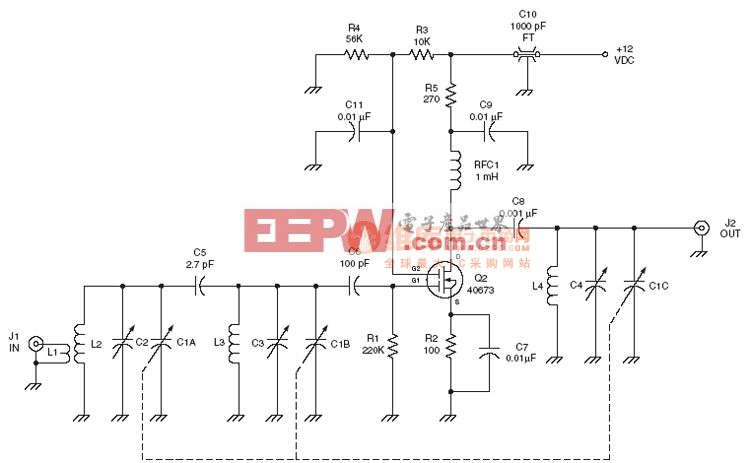

仿真中,采用QPSK調制,匹配濾波器滾降系數設為0.35,符號率為300 MHz,采樣率1.2 GHz,每個碼元采4個點,信噪比設為15 dB,信道為高斯白噪聲信道。

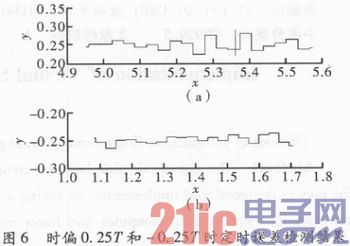

當時偏設為0.25T和-0.25T時,環路定時誤差檢測結果分別如圖6(a)和圖6(b)所示。通過圖8可以看出誤差檢測結果是可信的。

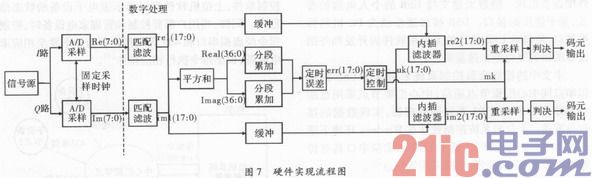

5 算法實現

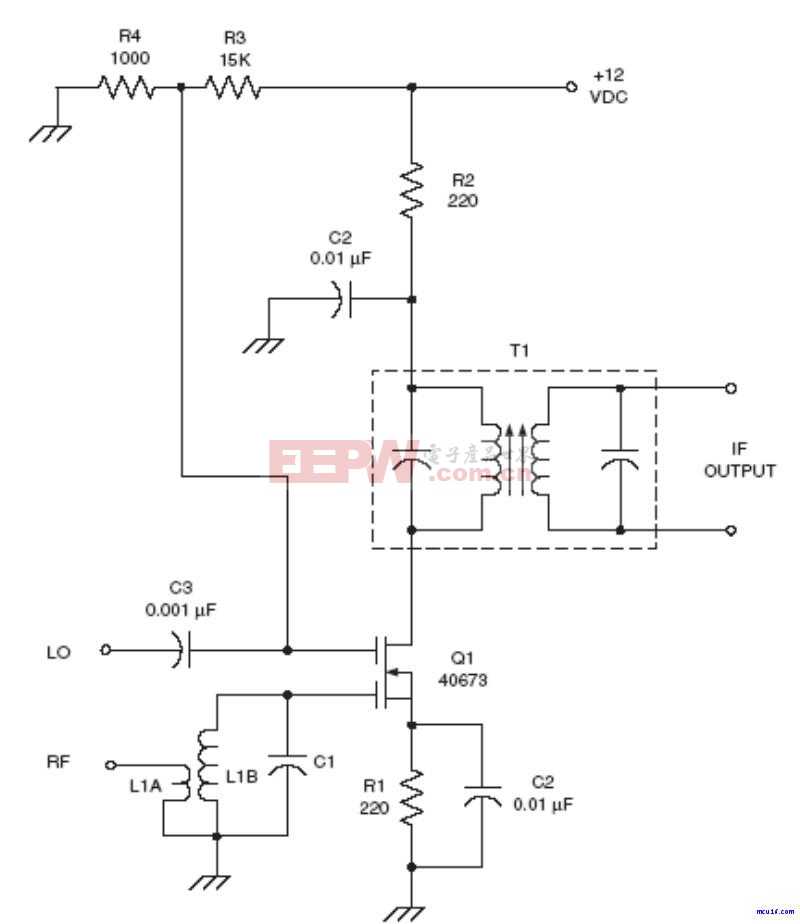

在Matlab仿真性能得到保證的前提下,文中對該算法進行了硬件實現,并取得了良好的效果。算法硬件實現流程,如圖7所示。

信號源部分使用信號發生器產生300 MHz的BPSK信號,A/D采樣率為1.2 GHz,A/D直接對基帶信號以4倍的符號率采樣,匹配濾波的滾降系數為0.5,數字處理部分采用Xilinx公司的Virtex-4系列FPGA芯片。算法實現消耗8%的Slices以及14%的DSP48s。

使用Chipscope觀察,當信噪比為15 dB時,定時同步前后的星座圖對比如圖8所示。

6 結束語

設計了基于數字濾波平方的全數字接收機定時同步方法,定時同步環路主要由定時誤差提取、定時控制與內插濾波器3部分組成。其中定時誤差是由基帶采樣信號進行離散傅里葉變換提取得到,并且文中設計了一種適用于高速通信下的并行實現結構,內插系數由定時控制模塊計算的小數間隔確定,從定時控制模塊計算出的整數間隔相當于重采樣時鐘,對內插后的信號進行采樣,即可得到同步數據。數字濾波平方法屬于非數據輔助型,對載波不敏感,可以先于載波同步進行,算法實現結構屬于前饋式,適合于突發通信、運算簡單、系統實現方便,Matlab仿真與硬件實現結果表明,該設計方案可以較好地解決定時問題。

評論