基于FPGA的光電編碼器接口設計

光電編碼器是許多傳感器和自動控制系統的重要部件,可用來測量位移、速度、加速度等。近年來在研究和使用方面,不斷有所創新和發展。由于光電編碼器具有精度高、體積小、重量輕、響應速度快、可靠性高、抗干擾能力強等特點,因此在國防、科研及工業自動化等領域應用越來越廣泛。

本文引用地址:http://www.j9360.com/article/201610/308363.htm在導彈的舵機伺服控制系統中,采用光電編碼器作為位置檢測裝置時,光電編碼器固定在電機軸上,并跟隨電機同軸轉動。為了減小舵機的體積,采用1個控制器控制4個舵機。舵機控制器采用DSP+FPGA的架構,DSP作為主控CPU,FPGA用于做接口處理。本文以Altera公司的型號為EP3C40F48417的FPGA為基礎,采用Verilog語言,設計了可與DSP相連的編碼器計數器接口,該接口具有數字濾波、方向鑒別、雙向計數、復位等功能。

1 光電編碼器原理

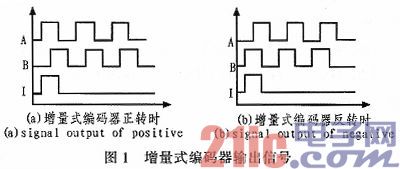

光電編碼器根據形成代碼方式不同,分為增量式和絕對式兩種。絕對式編碼器是直接輸出數字量的傳感器,在任何時刻編碼器的示值都是唯一固定的;增量式編碼器根據中心軸所轉過的角度,輸出一系列脈沖,典型輸出為兩個相位相差為90°的方波脈沖信號A、B和基準點定位脈沖信號I。增量式編碼器的A、B兩路信號的脈沖數標志著編碼器所轉過的角度,A、B兩路信號的相位關系標志著編碼器的轉向,A相超前B相90°時,編碼器正轉;A相滯后B相90°時,編碼器反轉;當I相輸出一個脈沖時,表示編碼器旋轉了一周。增

量式光電編碼器輸出信號如圖1所示。

由于光電編碼器的轉速隨時間可能發生不斷變化,所以脈沖周期T很難確定。但是在每個脈沖周期內,A、B兩相方波之間的相位關系是確定的。

2 FPGA設計

光電編碼器選擇MAXON公司的MR型編碼器,旋轉一周的脈沖數為500個。舵機的舵偏角范圍為±30°,速比為125。編碼器A、B兩相信號一個周期內信號產生四次變化,編碼器旋轉一圈對應的計數器值應為2000,所以當舵偏角從-30°到+30°變化時,計數值最大應為41667。FPGA與DSP相連的數據線為16位,最大數值為65536,計數器的初始值為32768,計數存在溢出的可能。所以每當舵機到達中心0°時,DSP發出復位指令,計數器值復位為32768,這樣在計數過程中就不會產生數據的溢出。為了減小干擾,A、B兩相信號計數之前要對其進行數字濾波。編碼器接口結構圖如圖2所示。

2.1 數宇濾波設計

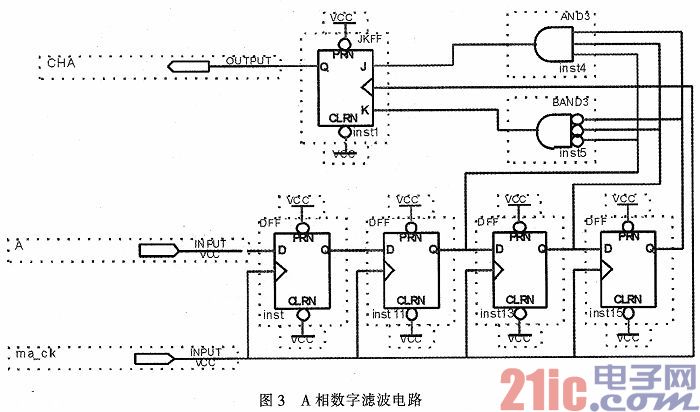

雖然編碼器輸出信號經過了硬件電路的前期處理,但是多數情況下仍然會產生噪聲信號,從而嚴重影響了計數的準確性,降低了整個系統的精度。為了消除噪聲信號,在FPGA內部設計了一個數字濾波器來濾除抖動脈沖,防止計數器的誤計數。數字濾波電路如圖3所示。

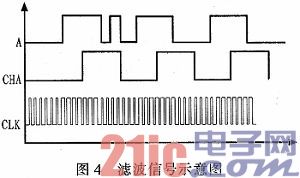

本設計采用4個D觸發器、一個JK觸發器和一些邏輯電路來實現濾波,原理為:A相信號經過4路D觸發器鎖存以后產生3路信號,3路信號相與之后作為JK觸發器的J端輸入,3路信號取反再做與邏輯之后作為JK觸發器的K端輸入。根據JK觸發器的原理計算各個時刻的信號輸出可知,當干擾信號頻率大于主時鐘頻率的1/3時,干擾信號將會被濾除掉。如圖4所示。A代表有干擾的編碼器信號,CLK為主時鐘信號,CHA為濾波之后的編碼器信號。

時鐘周期的選擇與干擾信號的脈沖寬的有一定的關系,要根據多次試驗結果確定干擾信號的頻率范圍,再結合編碼器信號的脈沖頻率合理選取,這樣才能滿足最后的要求,經過試驗確定主時鐘頻率為75 MHz,也就是說25 MHz以上的干擾信號不會對計數器產生影響。

2.2 計數器設計

實現計數的過程一般有兩種方法:一種方法是處理器內部定時計數器實現計數;另一種方法是由可逆計數器實現計數。第一種方法結構簡單,較為容易實現,但是不具有通用性,而且一個處理器上面的接口數量有限,無法對多個編碼器同時進行計數。后一種方案利用FPGA實現,具有較好的通用性,功能擴展方便,能夠對多個編碼器同時進行計數。

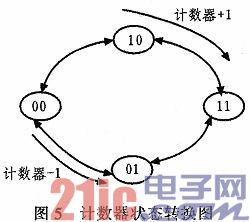

增量式編碼器根據軸所轉過的角度,輸出一系列脈沖,通過計數電路,對脈沖進行計數,得到相對的角位移。在脈沖周期T內,A、B兩相信號共產生四次變化,在每一次變化時計數器進行計數,這樣計數脈沖的周期減小到T/4,從而使光電編碼器的角位移測量精度提高4倍。

在采樣主時鐘的下降沿對A、B兩相信號進行采樣,采樣值與前一時刻的采樣值進行比較來判斷計數器的加減。當電機正轉時,A相超前B相90°,則在一個周期內,兩相信號共有四次相對變化:00→10→11→01→00,每發生一次變化,計數器便實現一次加計數,一個周期內共可實現4次加計數,從而實現正轉狀態下的四倍頻計數。當電機反轉時,A相滯后B相90°,則在一個周期內,兩相信號共有四次相對變化:00→01→11→10→00,每發生一次變化,計數器便實現一次減計數,一個周期內共可實現4次減計數,從而實現反轉狀態下的四倍頻計數。當沒有狀態轉換時,計數器不進行計數。如圖5所示。

采用D觸發器來進行旋轉方向的判斷,B相信號作為時鐘輸入,在B相信號的上升沿采樣A相信號的狀態,當輸出為高電平時,A相超前B相,表示電機正轉;當輸出為低電平

時,A相滯后B相,表示電機反轉。

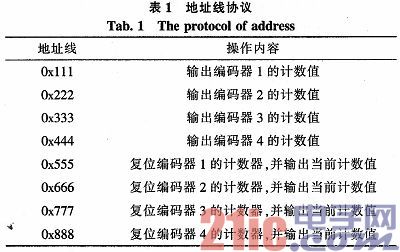

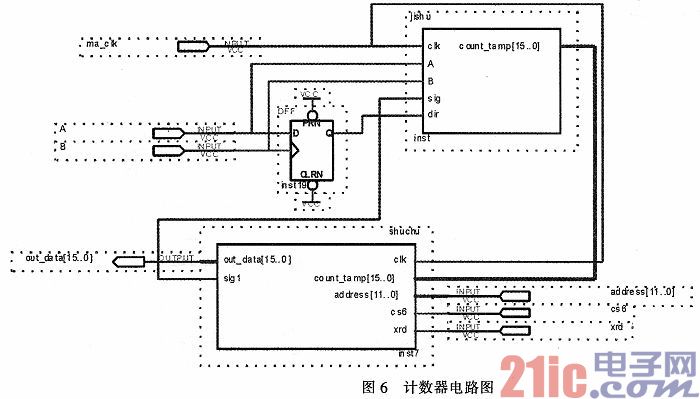

FPGA與DSP之間通過16位數據線、12位地址線,片選信號、時鐘信號和讀寫信號線相連。地址線上面不同的數據代表DSP對FPGA的不同操作,地址線協議如表1所示。計數器電路如圖6所示。

3 實驗結果

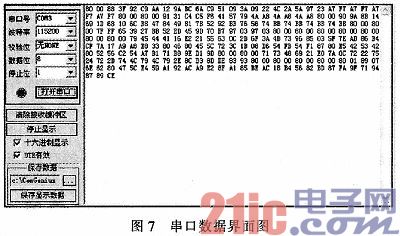

在實驗室條件下,DSP通過串口將計數值發送到計算機上,采用十六進制表示,串口協議如下:發送周期為10 ms,波特率為115200kbit/s,無校驗位,8位數據位,1位停止位。結果如圖7所示。

通過串口發出的數據可以看出,計數器的初始值為32768(十六進制為8090)。當電機正轉時計數器增加,當電機反轉時計數器減少,當電機停止旋轉時,計數器保持當前數值。可以根據DSP發出的復位指令,計數器復位到初始值32768。DSP和FPGA工作正常,DSP通過片選信號和讀信號能夠實時的讀取計數器的數值,能夠滿足電機控制的要求。

4 結論

從以上可以看出,利用FPGA設計光電編碼器的接口電路,減少了系統芯片的數量,僅用一片芯片即可完成整個系統的設計,降低了系統的功耗,縮小了系統的體積,提高了系統的可靠性和抗干擾能力,用Verilog設計電路,只需要修改程序語句即可,提高了系統維護和升級的便捷性。本文的設計方法結構簡單,無溢出,無誤碼,能夠準確的檢測碼盤位置的變化,運行可靠,能夠與DSP相連。

評論