一種基于FPGA的群路信號數字分路實現結構

由于具有高集成度、高速、可編程等優點,現場可編程門陣列(Field Programmable Gate Array,FPGA)已經被廣泛應用于中高速群路解調處理領域。數字分路技術是全數字群解調器的重要組成部分,也是群解調器實現過程中消耗硬件資源較大的部分,所以設計合理的分路實現結構將對整個解調器的處理速度和硬件開銷產生較大影響。目前,采用FPGA實現數字分路主要存在的問題是FPGA芯片中乘法器資源受限。因此,在已知硬件FPGA芯片乘法器資源約束條件下,設計更為有效的數字分路實現結構是目前重要的研究內容。

本文引用地址:http://www.j9360.com/article/201610/308361.htm1 算法結構

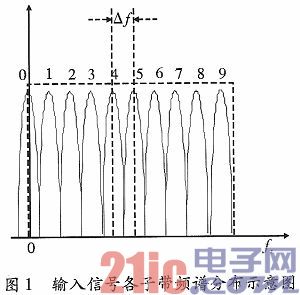

針對輸入信號各子帶在頻域中是按偶型堆積排列和均勻分割的,如圖1所示,可采用均勻DFT濾波器組實現其有效數字分路。在圖1中,輸入信號的基本參數如下:(1)每路載波的符號速率為R=2 Msample·s-1;(2)載波間隔為△f=3.2 MHz;(3)采樣速率為Fs=32 MHz。

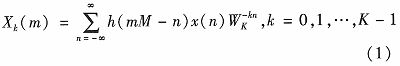

圖2給出了單個支路信號處理原理示意圖。輸入信號首先采用復指數序列e-jωk進行調制(其中,ωk=![]() ,k=0,1,2,…,K-1為第k個子帶的中心頻率,K為分路路數);然后再將調制后的信號經過低通濾波器進行濾波;最后將濾波后的信號進行降采樣(降采樣率為M),得到第k個子帶信號。該數學模型可表示為

,k=0,1,2,…,K-1為第k個子帶的中心頻率,K為分路路數);然后再將調制后的信號經過低通濾波器進行濾波;最后將濾波后的信號進行降采樣(降采樣率為M),得到第k個子帶信號。該數學模型可表示為

其中,x(n)表示輸入信號;h(n)表示分析濾波器;

;K表示分路路數;M表示降采樣率。根據這一數學模型,基于均勻DFT濾波器組數字分路技術,有基于多相結構和加權疊接-相加結構兩種實現結構。

由于輸入信號速率為32 MHz,各子帶頻率間隔為3.2 MHz,則分路路數K=32/3.2=10。又由于每路輸出信號速率為2×4=8 MHz,則降采樣率M=32/8=4,因此邏輯上可以按照K=M(其中,I=2.5)形式的多相結構實現數字分路。

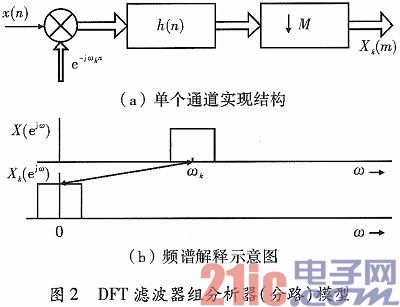

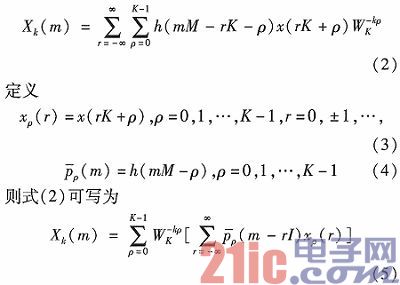

在式(1)中,通過變量置換n=rK+ρ,ρ=0,1,…,K-1,得到

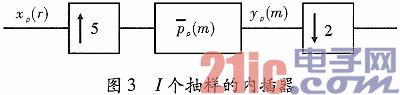

式(5)的括號中定義了一個I個抽樣的內插器,令yρ(m)是內插器的輸出,則該項對應的數學模型如圖3所示。

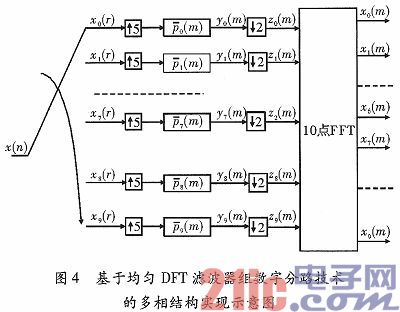

根據式(5)所示,則基于均勻DFT濾波器組數字分路技術實現結構如圖4所示,具體實現步驟如下

(1)對輸入信號x(n)進行10路并行轉換,得到10路子信號xρ(r),ρ=0,1,…,9,此時信號速率由fs=32 MHz變為f=32 MHz/10=3.2 MHz。

(2)對每一路子信號xρ(r)進行5倍速率內插,并分別采用對應的濾波器*

進行濾波,得到10路輸出信號yρ(m),每一路對應的濾波器

可以由分析濾波器h(n)按照式(4)得到,此時信號yρ(m)的速率由3.2 MHz變為3.2 MHz×5=16 MHz。

(3)對10路yρ(m)信號分別進行2倍下采樣,變為zρ(m)。

(4)對上述得到的10路并行信號進行10點FFT計算,得到分路后的10路信號。

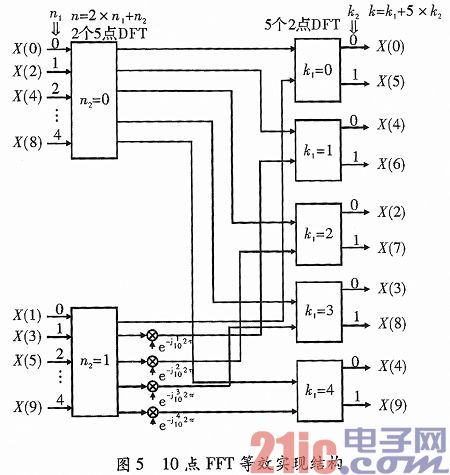

在圖4中,出現了10點FFT計算,為有效節省乘法器的資源,對10點FFT計算進行變換處理,分解為5點FFT的計算。10點FFT變換可表示為式(6)

由式(8)可得,一個10點的FFT運算可等效為一級5點FFT和2點FFT的級聯運算。具體實現框圖如圖5所示。

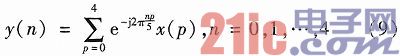

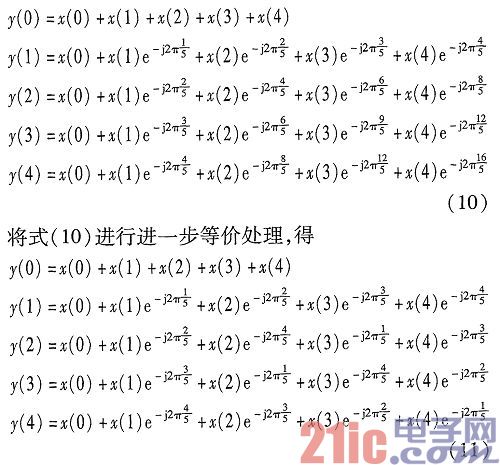

5點FFT變換可表示為

將式(9)展開,得

2 FPGA實現及測試結果

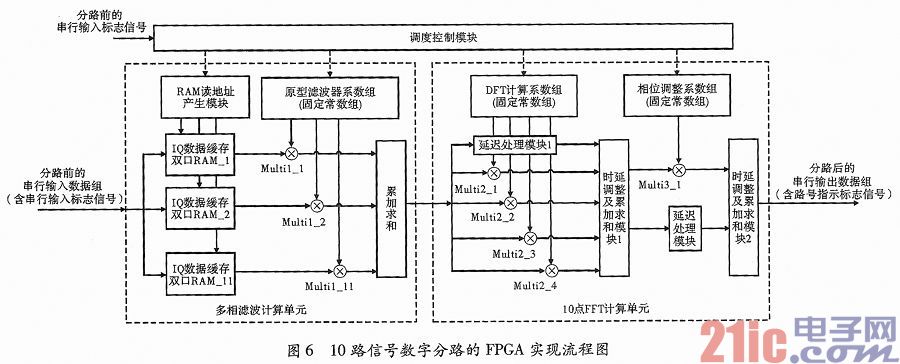

根據上述算法分析,結合FPGA資源與速度互換的處理思路,對10路信號的數字分路FPGA實現結構進行設計,具體處理流程如圖6所示。

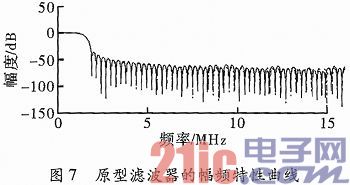

在圖6中,整個10路信號數字分路模塊共分為2大部分,第1部分是多相濾波計算單元,第2部分為10點FFT計算單元,兩個模塊在調度控制模塊的控制下工作。整個模塊的工作時鐘fclk=96 MHz,原型濾波器選用110階的匹配濾波器,濾波器的幅頻特性曲線如圖7所示。整個10點數字分路的FPGA處理流程如下。

(1)輸入信號同時進入11組并行工作的RAM存儲區,每進20個數據做一次流水處理,每個流水處理共有60個處理時鐘,共進行5次10點FFT計算;也就是說每進20個數,輸出50個數,每路5個點。

(2)調度控制模塊控制11個存儲RAM在每個時鐘周期產生11個不同數據,同時控制原型濾波器系數組產生11個多相濾波系數,11個數據和11個多相濾波系數進行相乘及累加產生1個FFT計算輸入點;每10個FFT計算輸入點組成1個10點FFT計算組,并用使能信號標識,串行送給10點FFT計算單元。

(3)根據10點FFT拆分為2個5點FFT和5個2點FFT計算流程及式(11)的數學計算公式,對多相濾波計算單元串行輸入的10個數據復制成相同的5組,第1組延遲4個時鐘周期輸出,第2~5組在調度控制模塊的控制下分時乘以不同的FFT計算系數,然后對5組輸出數據進行時延調整及累加求和,分別串行輸出2組5點FFT計算結果;對第1組數據在調度控制模塊的控制下分時乘以不同相位調整系數,對第2組延遲4個時鐘周期輸出;最后對2組輸出數據進行時延調整及累加求和,串行輸出10個FFT計算結果,并通過使能信號對10個FFT計算結果進行標識,使能信號的上升沿代表第1路數據。

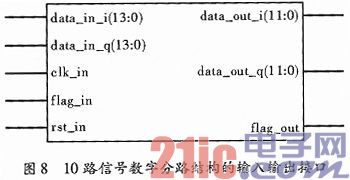

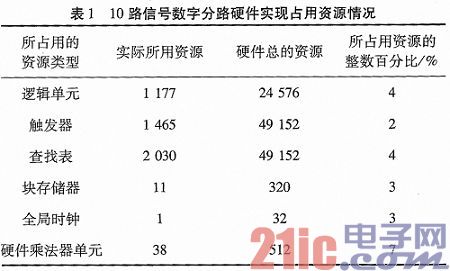

文中的10路信號數字分路結構在Xilinx的Vitex-4器件上實現,具體型號是xc4vsx55-11ff148,圖8給出了10路信號數字分路的輸入輸出接口,表1給出了算法的硬件資源占用情況。

3 仿真驗證及實際測試結果

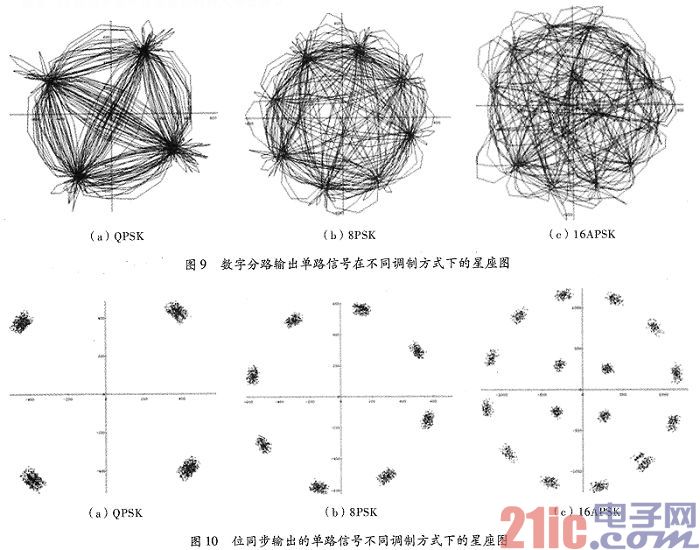

在ISE9.2.1環境下,采用VHDL完成了10路信號的數字分路模塊的開發,并采用ModeMm 6.2b軟件進行仿真驗證。同時,為驗證設計的10路信號的數字分路模塊的正確性,將10路信號的數字分路模塊連同解調模塊在搭建的測試系統中進行了實際測試。測試輸入信號源為10路QPSK信號,10路8PSK信號以及10路16APSK信號;測試輸出為10路信號的分路輸出星座圖及解調位同步后的星座圖。圖9為3種調制方式的分路輸出星座圖,圖10為3種調制方式位同步后的星座圖。

4 結束語

本文介紹了一種基于FPGA的10路信號的數字分路實現結構,在ISE9.2.1環境下,采用VHDL語言進行了實現,并在硬件平臺上對分路程序的性能進行了測試。該結構能夠有效降低FPGA的硬件資源消耗,尤其是乘法器的資源消耗,在全數字群解調器工程實現中有著良好的應用前景。

評論