基于1553B總線遠程終端的FPGA程序設計

0 引言

本文引用地址:http://www.j9360.com/article/201609/303476.htm1553B總線是MIL-STD-1553美國軍用標準總線的簡稱,在飛機的航電系統中應用廣泛.為了提高可靠性,1553B 總線一般采用雙余度總線結構,在1553B 總線上可掛接三種終端類型:總線控制器(BC).遠程終端(RT)和總線監視器(BM).總線網絡上可掛接32 個終端,在這32 個終端中,遠程終端的數量往往最多.目前,為實現1553B 總線通信,大都是開發獨立的通信接口模塊,不但成本高,整個系統的重量也會因此增加,不利于航空領域的使用.隨著電子技術的發展,FPGA已經迅速應用于各個領域,系統中的各個電路模塊大都包含FPGA 芯片.本文介紹一種使用FPGA 編程,實現1553B總線通信中遠程終端的方法,本方法具有開發周期短.方法簡單.可移植性強的特點,可大大降低系統的開發成本,縮短開發周期.

1 1553B總線簡介

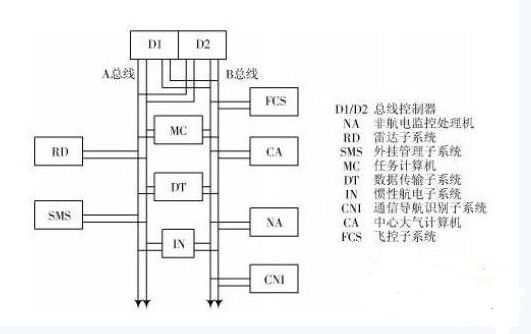

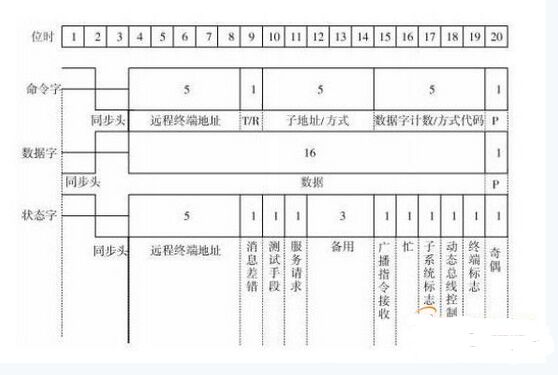

現代飛機典型的航電系統及1553B 總線應用框圖如圖1所示.1553B總線采用指令/ 響應型通信協議,構成1553B 總線傳輸協議有三要素:命令字.數據字和狀態字,每個字的長度為20 b,且由3部分組成:同步頭(3 b).數據段(16 b)和奇偶位(1 b),如圖2所示.

命令字由總線控制器(BC)發出,共包含20位的長度,前3位是同步頭,最后一位是奇偶校驗位,有效信息為16位,有效信息位中,前5位為RT 的地址場,該場指出了被尋址的終端地址.有1位是發送/接收(T/R)位,當此位為“1”時,命令被尋址的終端發送消息,為“0”時,則命令被尋址的終端接收消息.另外5位為子地址/方式代碼場,一般情況下,按指示向被尋址終端某一個分地址進行通信,當這5位全為“0”或全為“1”時定義為方式代碼場.有效信息中的最后5位為計數/方式碼場,通常情況下,它定義了與該指令相關的數據字數,但在前5位為方式場時,它就成了方式控制碼.

數據字有20 位長,其中16 位有效信息是總線上傳輸的數據信息.

狀態字僅僅對指令字響應,被尋址的遠程終端發出,并包括5位本RT地址場和8位指示了通信狀態和本RT及子系統狀態的信息位.

2 硬件構成

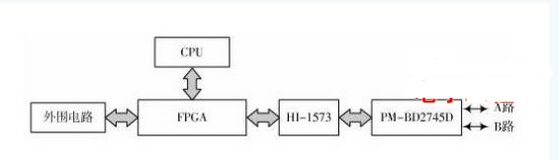

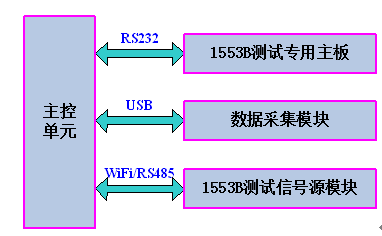

信號調制解調所需的隔離變壓器和收發器需單獨購買,本文采用HOLT 公司的PM-DB2745D 芯片和HI-

1573 芯片,從而曼徹斯特編碼解碼往后的部分都可以在一片FPGA芯片內實現.本文是將1553B總線的遠程終端集成到海軍某型號飛機航電子系統的一塊計算機板上,計算機板采用的是Altera 公司的Cyclone Ⅲ系列FPGA芯片,硬件連接關系如圖3所示.

3 FPGA內部模塊構成

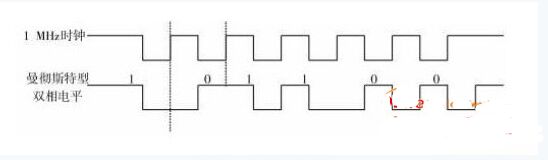

遠程終端是用戶子系統到數據總線上的接口,它在BC 的控制下提取或吸收數據,總線上的位傳輸速率為1.0 Mb/s,信號以串行數字脈沖調制方式在數據總線上傳輸,傳輸的數據碼為曼徹斯特Ⅱ型雙電平編碼,邏輯1為雙極編碼信號1/0(即一個正脈沖繼之以一個負脈沖),邏輯0 為雙極編碼信號0/1(即一個負脈沖繼之以一個正脈沖),過零跳變發生在每一位時的中點,如圖4所示.

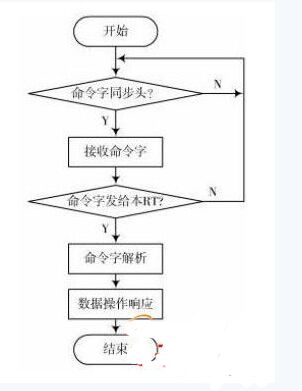

總線系統中傳輸的消息格式有10種,本文涉及到的有三種消息傳輸方式,即總線控制器向遠程終端的傳輸.遠程終端向總線控制器的傳輸和遠程終端向遠程終端的傳輸.FPGA的主要編程思路如圖5所示.

實際編程時,對1553B總線數據的解析響應在數據解析模塊.數據編碼模塊.主控模塊和軟件接口模塊的協調工作下完成,FPGA 內部各功能模塊的聯系如圖6所示.

FPGA中各模塊的詳細功能詳述如下:

(1)數據解析模塊:本模塊對總線上串行數字脈沖進行接收并解析,數據解析模塊負責檢測命令字.數據字.狀態字的同步頭,1553B 總線的每一條消息都是從命令字開始的,數據解析模塊在檢測到命令字同步頭后,將同步頭后邊的16位有效信息進行串并轉換,經過解析后,判定是否對該命令做出響應,若此命令是發給本RT終端的,則根據命令做出接收數據或發送數據的響應,若此命令不是發給本RT 終端的,則不做出任何響應.

(2)數據編碼模塊:本模塊在接收到數據發送命令時進行工作,主要完成對發送數據的曼徹斯特Ⅱ型雙電平編碼.

(3)主控模塊:本模塊控制各模塊協調工作,為各模塊提供正常工作的時鐘信號,當數據解析模塊接收到的是接收數據命令時,將數據解析模塊解析得到的數據字存儲到一個雙口RAM中,記為RAM1,等待CPU前來讀取,RAM1 被劃分為32 個區域,對應此RT 終端的32 個子地址;當數據解析模塊接收到的是發送數據命令時,將CPU事先存儲在另一個雙口RAM中的數據發送給數據編碼模塊,此雙口RAM 記為RAM0?RAM0 同樣被劃分為32個區域,對應RT終端的32個子地址.

(4)軟件接口模塊:本模塊是與CPU 通信的接口,當RAM1中某個區域存儲新的數據時,通知軟件前來讀取,當軟件向RAM0中某個區域寫入數據后,通知FPGA軟件寫入數據完畢.

4 試驗

試驗時,將程序下載至FPGA中,使用Quartus Ⅱ軟件自帶的邏輯分析儀觀察FPGA的通信性能,采用上海旋極公司提供的成品1553B 板卡和配套測試軟件與本文開發的電路進行通信,試驗證實:兩者通信結果正確無誤,滿足1553B總線通信要求,其中,A路總線接收數據的邏輯關系如圖7所示.

評論