基于SM61580的MIL-STD-1553B總線終端設計

摘要:通過對MIL-STD-1553B總線的研究,實現遠程終端(RT)與總線控制器(BC)之間高效、可靠的數據通信,提出了一種基于SM61580的MIL-STD-1553B總線終端設計方案。選用SM61580芯片,利用SM7C133存儲功能,并結合MSP430F247的控制優勢,采用透明模式連接芯片與處理器,實現1553B總線終端設計。該1553B總線終端系統的應用具有普遍的實用性。

關鍵詞:1553B總線;SM61580;MSP430F247;終端

MIL-STD-1553總線是美國國防部制定的一種具有可確定性且傳輸可靠的數據總線,被廣泛應用于軍用飛機、軍用車輛以及艦載等領域中。1553B終端系統可以使用8位單片機,16位單片機,32位單片機來實現。本設計選用SM61580接口芯片,設計了基于MSP430F247單片機的硬件接口電路,完成了軟件接口程序,最終實現了1553B終端(RT)與總線控制器(BC)之間高效、可靠的數據通信。

1 MIL-STD-1553B總線

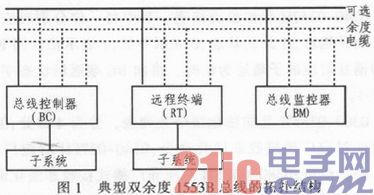

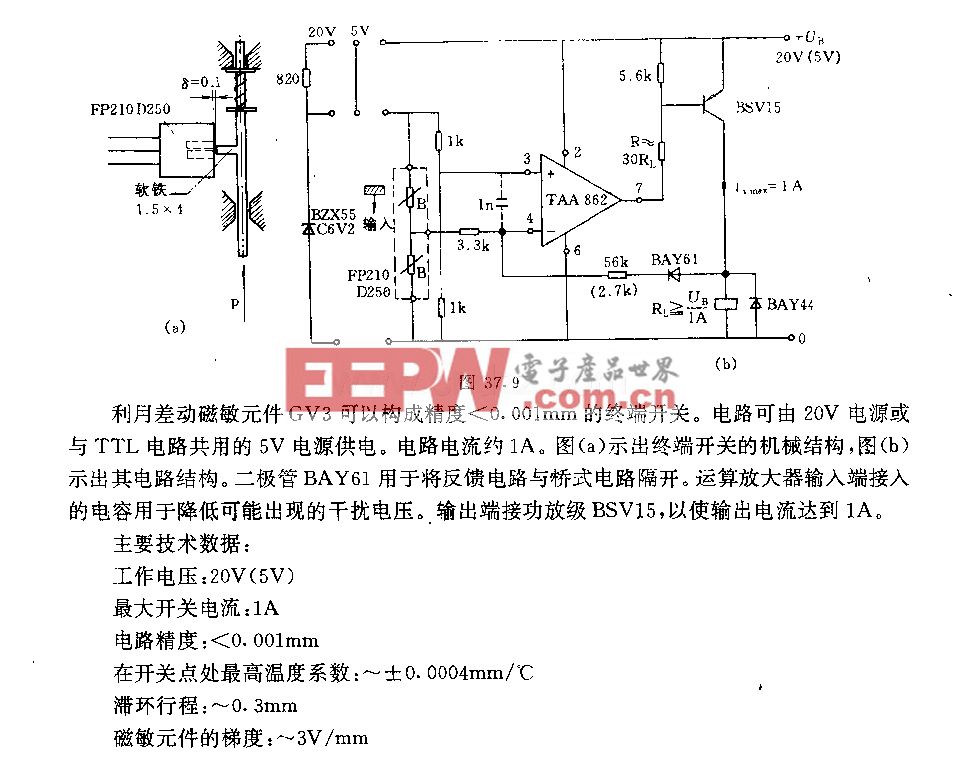

1553B總線網絡由終端、子系統和總線傳輸介質組成,結構如圖1所示。終端是使數據總線與子系統相連接的電子組件。子系統為從多路數據總線上接收數據傳輸服務的裝置或功能單元。總線控制器(BC)是總線系統組織信息傳輸的終端。總線監控器(BM)是總線系統中指定做接收且記錄總線上傳輸的信息并有選擇地提取信息以備后用的終端。遠程終端(RT)是總線系統中不作為總線控制器或總線監控器的所有終端。

1553B總線的傳輸速度是1Mb/s,采用曼切斯特Ⅱ編碼,半雙工工作方式。1553B總線有10種消息格式,每個消息至少包含兩個字,每個字包含有16個信息位、一個奇偶校驗位和3個位長的同步頭。適用于變壓器耦合的曼切斯特II編碼,通過雙絞線可靠傳輸的長度可以超過30 m。

2 SM61580芯片的功能特點

SM61580為微處理器和1553B總線之間提供了完整、靈活的接口電路。

SM61580芯片包含兩個低功耗收發器和一個全雙工譯碼/編碼器,一個完整的BC/RT/MT(總線控制/遠程終端/監視模式)多協議邏輯電路,存儲器管理電路和中斷邏輯電路,4Kx16bit共享靜態RAM,以及一個靈活的緩沖接口與主處理總線相連。

SM61580的內部地址鎖存器和雙向數據緩沖器,可直接與主處理器總線相連,支持16位和8位的微處理器,并可與處理器共享一個緩沖RAM。

SM61580還可通過DMA接口電路與一個16位處理總線相連。

SM61580有3種監控模式:字監控(word monitor),選擇信息監控(selective message monitor),遠程終端與選擇監控組合(combined RT/selective monitor)。

3 SM61580內部RAM資源分配

SM61580內部具有4Kx16共享RAM。在RT增強模式中,兩個堆棧指針分配在固定的位置:0100H是堆棧指針A的地址;0104H是堆棧指針B的地址。0000-00FFH是256字的堆棧A空間,也是1553B接收信息描述符區,每個描述符占4個字,一共可儲存64個描述符。描述符的4個字分別是塊狀態字、時間戳,接收數據塊指針、接收命令字。

0108-010FH是模式命令選擇中斷表,設置每一個接收、發送、廣播接收、廣播發送的模式命令時,是否產生中斷。

0110-013FH是模式命令返回數據的固定地址,當RT接收到一個模式命令時,將儲存于對應位置的數據自動返回給BC。

0140-01BFH和01C0-023FH分別是RT的A/B區域地址查詢表。對于A區域,地址分為4部分:0140-015FH分別對應子地址0到子地址31的接收數據緩沖區的首地址;0160-017FH分別對應子地址0到子地址31的發送數據緩沖區的首地址;0180-019FH分別對應子地址0到子地址31廣播模式數據緩沖區的首地址;01A0一01BFH分別對應子地址0到子地址31的子地址控制字,可以設置數據緩存區的大小和工作方式,如:單消息模式、雙緩沖模式和循環緩沖模式。

0240-0247H是忙位查詢表,其中每一位分別對應子地址0到子地址31的忙狀態,0表示不忙,1表示忙。當RT收到的消息對應的子地址為忙時,將向BC端返回狀態字的忙位置1。

0300-03FFH是非法化指令查詢表,分為4部分:0300-033FH對應廣播接收非法化命令;0340-037FH對應廣播發送非法化命令;0380-03BFH對應非廣播式接收非法化命令;03C0-03FFH對應非廣播式發送非法化命令。當RT收到非法化命令字時,將向BC返回對應的狀態字。

0260-02FFH和0400-0FFFH為數據緩存區。這部分空間可以由子地址0到子地址31的子地址控制字設置每個子地址對應的數據緩存區空間的大小和工作方式。

4 SM61580與MSP430F247的接口設計

4.1 硬件接口設計

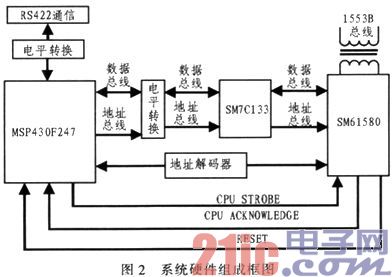

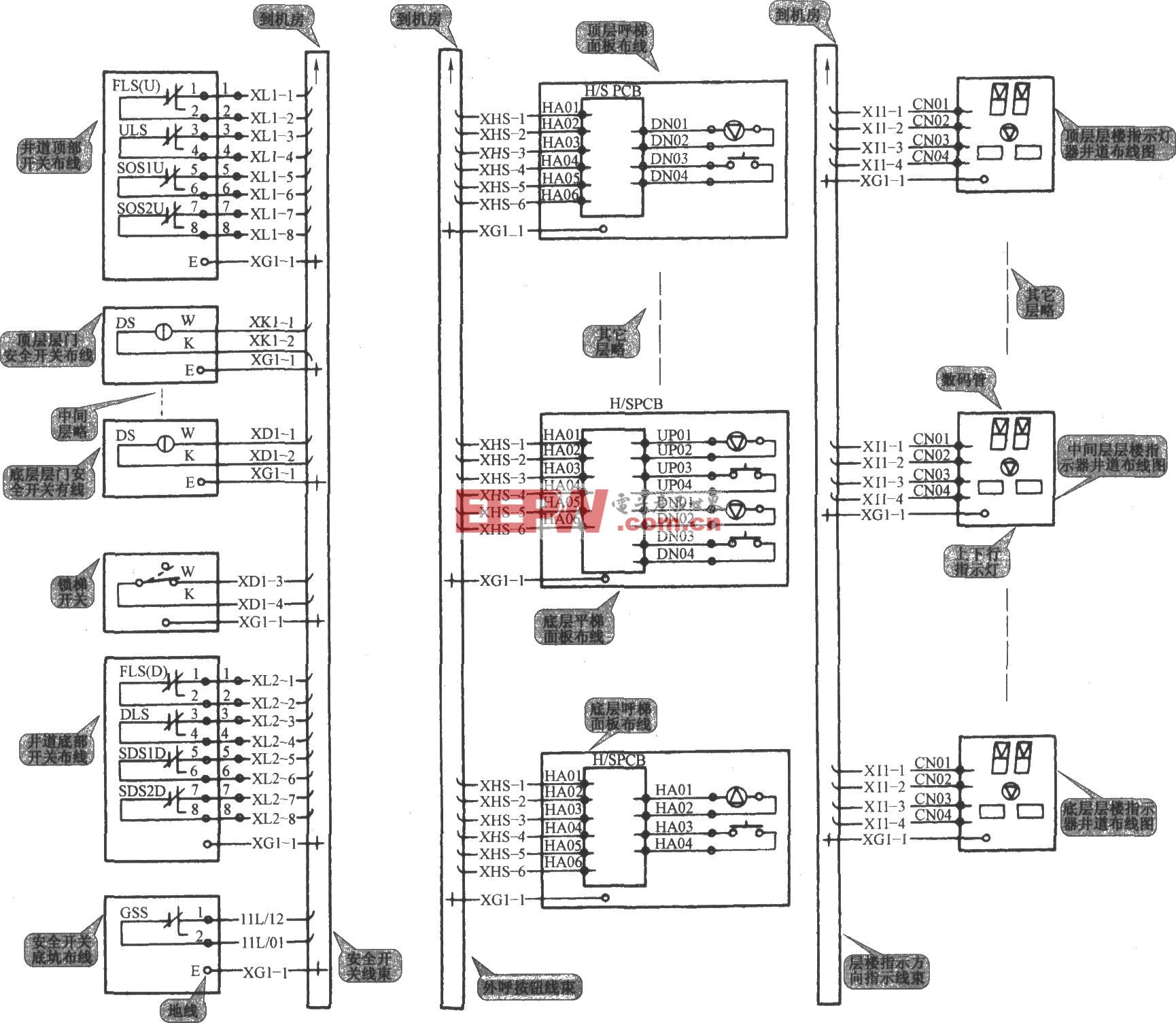

SM61580與16位處理器的連接方式采用16位透明模式。透明模式使用外部雙端RAM,這使得主處理器能迅速的訪問RAM(只受到RAM的速度限制);在這種模式下,可消除SM61580的調整延時。系統框圖如圖2所示。

在雙端RAM的接口,RAM的一端由主CPU訪問,另外一端可為SM61580通過存儲器的控制信號,由1553B邏輯電路訪問。地址和數據總線需要三態緩沖器來為CPU訪問SM61580的內部寄存器。SM61580輸入信號MEN/REG直接與邏輯0信號相連,SELECT與地址解碼器輸出1553REGSELECT相連,從而進行寄存器訪問操作。

引腳RTAD4-0和RTADP通過跳線可以選擇SM61580的地址編號。芯片采用外部接16 MHz晶振工作方式。

其中雙端RAM采用的是SM7C133。

SM7C133是一款高速CMOS雙端口靜態RAM,容量為2Kx16bit。

SM7C133有兩組獨立的端口、地址、I/O管腳,并且在進行讀或寫操作時異步訪問存儲器。CE是自動低功耗的控制端,允許對應端的片內電路進入待機功耗模式。

SM7C133有2組獨立的端口,包括地址線、I/O線,控制線,可以單獨訪問存儲器進行讀寫操作。SM7C133中CE是自動低功耗的控制端,當沒有選擇(CE=1)時,各端口進入待機模式。當某端口的CE使能時,可以訪問整個存儲陣列。

為了保證寫操作有效,數據必須在WR/的上升延之前建立并持續。寫操作由SDtWR/管腳和CE管腳控制。2個WR/管腳用來分別控制IO口的高字節與低字節。

如果一個端口寫數據到一個地址,而另一個端口試圖去讀這個地址,數據必須經過一個端口到端口的流通延時,才可以在輸出端口被讀出,否則,讀出的數據是不確定的。

微控制器選用MSP430F247單片機,其特點如下:強大的處理能力;超低功耗;系統工作穩定;豐富的片上外圍模塊。

為了在開發過程中驗證1553B總線終端傳輸數據的正確性,終端上制作了RS422接口,便于計算機顯示總線上的收、發數據。

4.2 軟件接口設計

SM61580內部具有25個寄存器,包括17個通用控制寄存器和8個測試寄存器。其中,設置17個通用控制寄存器是軟件接口設計的關鍵。

設置啟動/復位寄存器,先進入復位狀態;設置配置寄存器3,進入增強模式;設置中斷屏蔽寄存器,使能消息結束中斷;設置配置寄存器2,進入增強型RT存儲器管理模式;設置配置寄存器3,增強模式允許。設置配置寄存器1,進入RT工作方式,開啟RT。

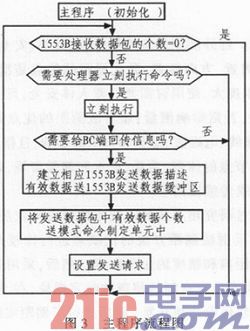

主程序對1553B信息的處理采用中斷處理方式。從BC端發送來的1553B命令有2種要求:不需要RT回傳數據和需要RT回傳數據。

1)不需要RT回傳數據

BC端發送命令字為非模式命令,要求RT接收信息,單片機終端收到信息進入中斷程序,設置相應的任務標志,然后進入主程序,根據155 3B接收信息描述符區中接收數據塊指針,找到1553B接收數據緩沖區,然后執行這些數據對應的任務,然后在主程序循環等待下一次中斷。

2)需要RT回傳數據

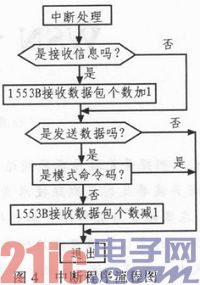

首先BC端發送命令字為非模式命令,要求RT接收信息,單片機終端收到信息進入中斷程序設置任務標志,然后進入主程序,找到1553B接收數據緩沖區,執行相關任務,并把需要返回給BC端的數據準備好,保存在1553B發送數據緩沖區,且將需要回傳數據字個數保存到模式命令對應的地址單元,然后設置服務請求,將配置寄存器1中的第9位設為0。與此同時,BC端向RT一直發送空指令,得到相應的返回狀態字,判斷狀態字的第11位,若為1,表示RT將數據準備好,BC向RT發送模式命令,命令編碼為10000,即為發送向量字命令,要求RT發送消息。RT收到模式命令后,返回狀態字,且將準備好的數據個數返回給BC;然后BC端再發送一次非模式命令,要求RT發送消息,數據個數為剛才收到的返回值。此時,BC端再次收到返回的狀態值和RT回傳的有效數據。基于SM61580的單片機終端系統程序流程圖如圖3、圖4所示。

5 結論

文中重點介紹了SM65180接口芯片的功能特點和RAM資源。并且給出了基于SM61580的MIL-STD-1553B單片機終端系統的硬件和軟件設計方法。在多次的系統調試試驗中,RT終端系統與BC總線控制器之間實現了高效、可靠的數據通信。該1553B總線終端系統的應用具有普遍的實用性。

評論