基于CS5451A多路同步數據采集系統設計

摘要:針對目前低電壓等級的繼電保護以及測控裝置對數據采集的高精度、低成本的要求,提出一種多路同步數據采集系統的設計方案。該方案采用MPC8313為主控制器,CS5451A為模數轉換器,通過對CS5451A Master模式串口輸出時序以及FIFO讀寫時序的研究,在CPU和CS5451A之間設計了一個串并轉換模塊實現采樣數據的接收,數據接收后存入FIFO緩沖區,這樣解決了利用處理器SPI接口直接接收數據CPU占用率高的矛盾。

關鍵詞:FPGA;異步FIFO;模數轉換器;CS5451A

繼電保護或者測控裝置都需要同步采集多路的電壓或者電流信號,現在一般的實現方式都是用多路逐次逼近型ADC(譬如AD7656或者ADS8-556)實現多路同步數據的采集,這種方案采樣速度高、控制簡單,但是每一通道都需要基于運算放大器的抗混疊濾波器,所以實現起來成本高、占用PCB面積大。本文提出一種使用CS5451A模數轉換芯片實現多路同步數據采集的實現方案,這種實現方式電路簡單、成本低。在本方案中,處理器選用的是飛思卡爾MPC8313處理器,主頻333 MHz。CS5451A如果用CPU直接控制,由于CS5451A芯片輸出數據速率低,處理器與ADC速度嚴重失配會大大占用CPU的開銷,本文提出一種利用XILINX可編程邏輯芯片FPGA實現異步FIFO和串并轉換模塊來實現采樣數據的接收的方法,串并轉換模塊只需要接收一幀數據,存到異步FIFO后,向CPU發出一個中斷信號,在中斷服務子程序中CPU讀走FIFO中的數據,這樣可以大幅度提高CPU的利用率,系統結構簡單,易于實現。

1 CS5451A概述以及電路的設計

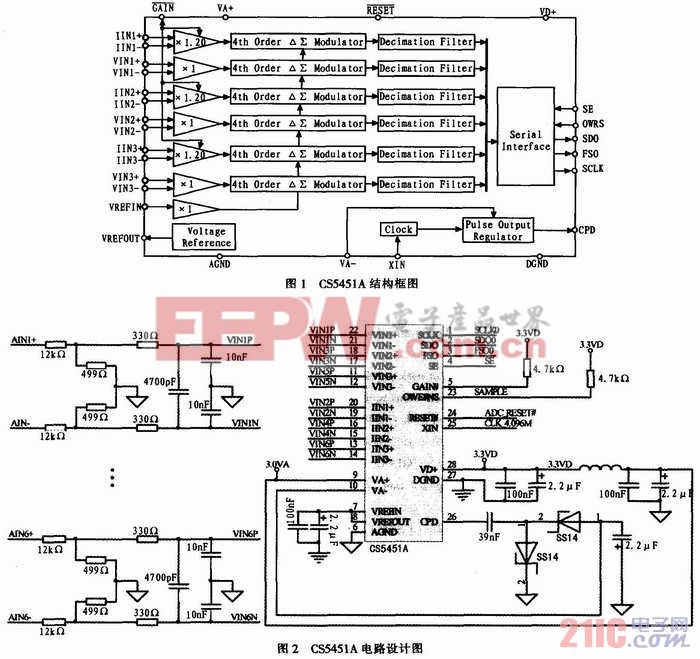

CS5451A是Cirrus Logie公司設計的一款高度集成的模數轉換芯片。在一個硅片上集成了6個△-∑A/D轉換器,6個數字濾波器和一個與微控制器或DSP相聯接的串行接口。CS5451A包括3個電壓測量通道、3個電流測量通道,它們的主要區別是3個電流測量通道的運算放大器的增益是可以更改的,可以設置成1倍或者20倍,而電壓通道的增益固定為1倍。由于△-∑A/D轉換器采用過采樣技術以及數字濾波器,所以簡化了ADC前級的抗混疊濾波器的設計。在本設計中抗混疊濾波器只設計了1階低通濾波器。CS5451A結構框圖如圖1所示。

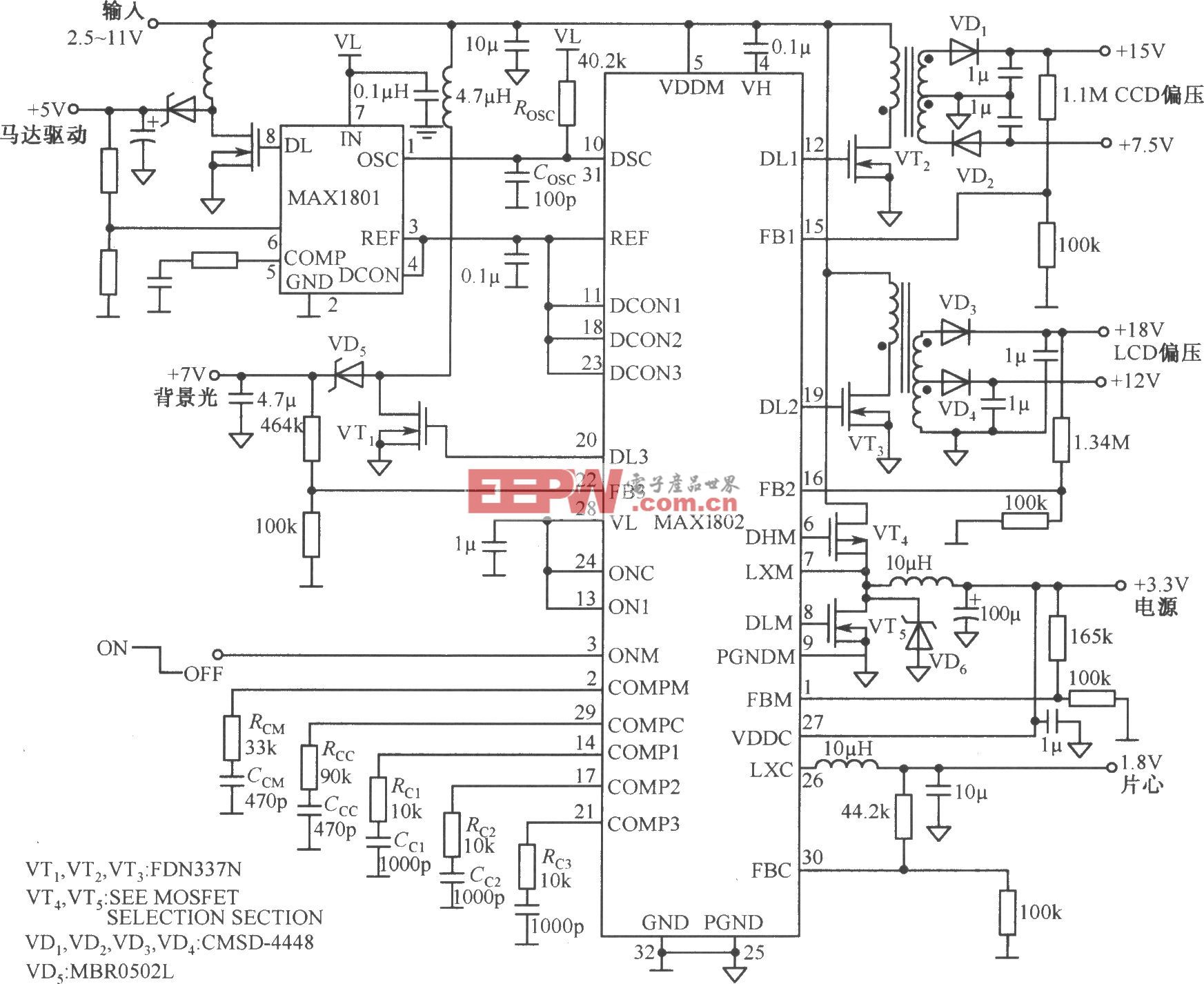

在本設計中CS5451A的配置如下:

1)ADC電流通道增益設置為1倍增益,這樣,6個通道增益都為1,電流通道和電壓配置一樣,每一通道不再有區別,容易做成通用的模擬輸入設計。

2)最大輸入范圍為+20 V,互感器輸出的電壓信號通過電阻分壓網絡產生一個最大為±800 mV的電壓信號,通過一介低通濾波器進入ADC芯片,CS5451A電路設計如圖2所示。

3)使用內部1.2 V參考電源。

4)時鐘輸入為4.096 MHz。

5)數據輸出速率4.0 k還是2.0 k由CPU控制。

評論