基于FPGA的多路CameraLink數據的WDM光傳輸

一、系統總體介紹

本系統是基于FPGA的多路CameraLink數據的單光纖傳輸設計,由于FPGA的開發成本低廉,升級方便所以成為該系統設計的選擇。

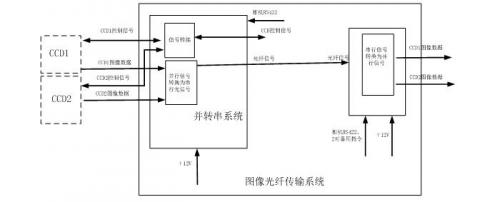

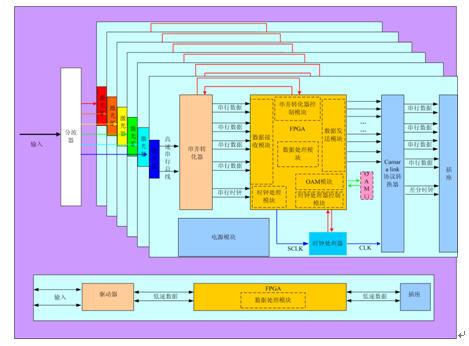

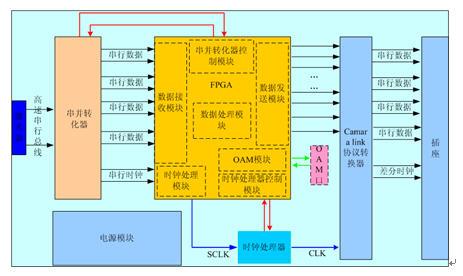

圖像光纖傳輸系統主要由并轉串系統和串轉并系統組成,系統組成的框圖如圖1.1所示。

并轉串系統將兩臺CCD的并行圖像數據轉換為串行光信號,經光纖傳輸后發給串轉并系統,串轉并系統將光信號再恢復成兩臺CCD的并行圖像數據。光纖上傳輸的圖像數據速率在1.4G-2.8G內可調。

圖1.1系統組成的框圖

二、系統工作原理和組成

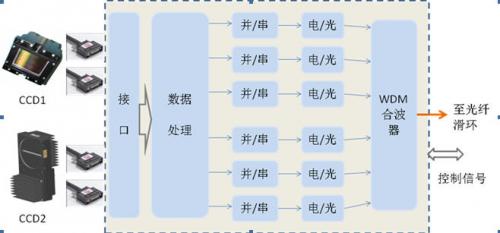

基于成本和實現難度的考慮,主要的工作原理是采用電路并串變換+光波分復用(WDM)的方式實現超大容量數據合成,完成數據通過一根光纖傳輸的功能。也就是先將每一組Camera link 數據進行并串變化,形成一路串行信號,之后通過WDM技術將各路串行信號的各個波長通過光路合成到一根光纖當中,經過傳輸后(主要是經過光纖),在接收端還原成各個波長,經過處理后恢復出原始信號。

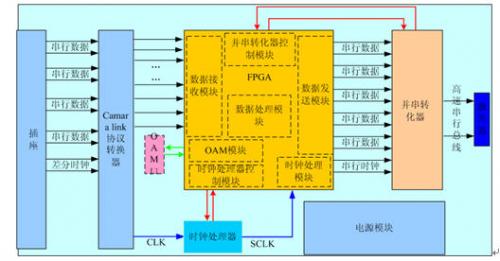

系統基本組成如下圖所示。兩個可以full配置的CCD攝像頭分別通過兩條26芯標準電纜將圖像數據傳給本系統。每個Camera Link數據組X、Y和Z分別通過接口進入系統,并完成并串轉換、電光轉換、合波等,最后統一到一根光纖。經過光纖傳輸后,再由接收部分經過分波器、光電轉換、串并變換和輸出接口后,恢復為同從CCD接收到的原始數據完全相同的格式,再通過四條26芯標準電纜將數據輸出給下級處理設備。

圖2.1 系統組成框圖

三、實現方案

3.1總體思路

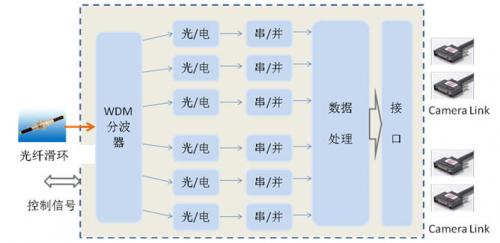

圖3.1 系統方案框圖

系統采用電路串并變換+光波分復用(WDM)的方式實現超大容量數據合成的方式,完成數據通過一根光纖傳輸。系統的構成如圖3.1所示。

系統分為發送部分單元和接收部分單元。發送部分單元和接受部分單元又各分為高速部分模塊和低速部分模塊兩部分。高速部分模塊獨立完成數據的串化、解串化工作;低速部分模塊完成相關數據和控制信號的處理。

發送部分單元高速電路完成六路Camera link 總線(兩個CCD full配置的數據量)的串化,把每一路camera link 總線的數據串化后,送入激光器變成光信號,再用波分復用的形式通過一根光纖傳送出去。發送部分總體框圖如圖3.2所示。

圖3.2 發送總體框圖

接收部分單元高速電路完成六路camera link 總線 (兩個 CCD full配置的數據量)的解串工作,首先通過波分解復用系統分出每一路camera link 總線的數據,然后再把每一路串化的camera link 數據解串,恢復成標準的并行信號。接收部分總體框圖如圖3.3所示。

圖3.3 接收總體框圖

在系統地評估產品的復雜性和可靠性的需求后,我們決定選用Xilinx Spartan3E系列產品作為FPGA核心模塊的首選器件。Xilinx 3E系列產品價格較低,功能全面,是世界上暢銷的 FPGA。

3.2發送部分單元

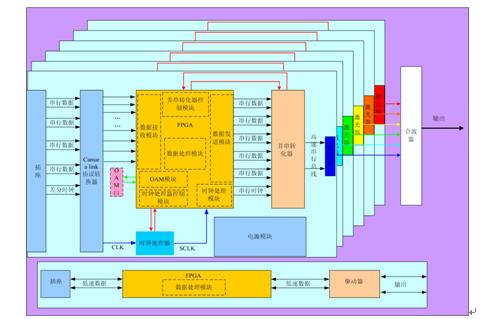

發送部分單元高速電路完成六路Camera link 總線(兩個CCD full配置的數據量)的串化,把每一路camera link總線的數據串化后,送入激光器變成光信號,再用波分復用的形式通過一根光纖傳送出去,發送單元電路模塊整體框圖如圖3.4所示。

圖3.4 發送單元電路模塊整體框圖

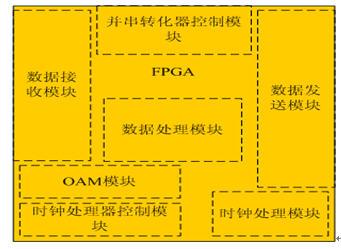

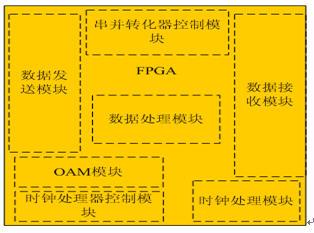

發送單元包含如下幾個模塊,如圖3.5所示:

發送單元數據接收模塊:完成正確接收來自Camera link 協議轉化器的數據的功能;

發送單元數據處理模塊:完成發送數據的核心處理功能;

發送單元數據發送模塊:完成正確將合成的數據以和Serdes匹配的形式發送到serdes的功能;

發送單元并串轉化器控制模塊:完成對并串轉化器的OAM功能;

發送單元時鐘處理模塊:實用內部的時鐘部件完成時鐘的相應處理,比如分頻、倍頻、相位調整等;

發送單元時鐘處理器控制模塊:完成對時鐘處理器的OAM的功能;

發送單元OAM模塊:和上層控制管理器配合,完成發送系統的OAM工作。

圖3.5 發送單元模塊劃分

下面詳細介紹發送部分單元模塊具體功能及實現:

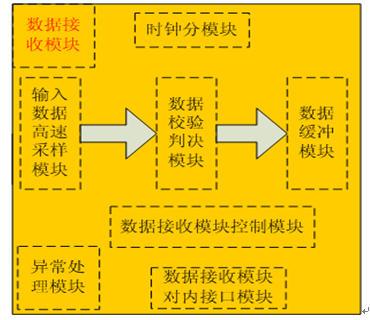

發送單元數據接收模塊完成數據的正確接收、判決和緩沖的功能。模塊內部邏輯框圖如圖3.6所示。包括輸入數據高速采樣模塊、數據校驗判決模塊、數據緩沖模塊、數據接收模塊控制模塊、數據接收模塊對內接口模塊、異常處理模塊和時鐘分模塊。

圖3.6 發送單元數據接收模塊內部邏輯框圖

數據緩沖模塊:對數據校驗判決模塊產生的數據進行緩沖,提高數據的可靠性和系統的安全性,出現溢出或者空閑的時候上報相關信息給數據接收模塊控制模塊便于OAM。

異常處理模塊:提供不可預測的異常處理,比如復位等,以提高系統的可靠性和穩定性。

時鐘分模塊:提供本模塊需要的時鐘。異常處理模塊不需要時鐘;數據接收模塊對內接口模塊時鐘為OAM模塊工作時鐘;數據接收模塊控制模塊為異步,不需要時鐘;輸入數據高速采集模塊和數據校驗判決模塊采用線路時鐘的3倍頻或者6倍頻時鐘;數據緩沖模塊采用線路時鐘的頻率。

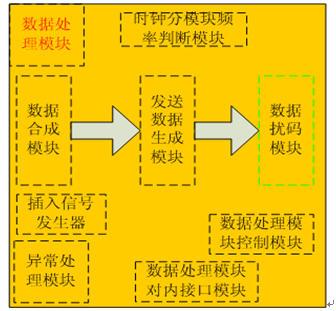

發送單元數據處理模塊完成核心的數據產生的功能。模塊內部邏輯框圖如圖3.7所示。包括插入信號發生器、數據合成模塊、發送數據生成模塊、數據加擾模塊、數據處理模塊控制模塊、數據處理模塊對內接口模塊、時鐘分模塊和異常處理模塊。

圖3.7 發送單元數據處理模塊內部邏輯框圖

插入信號發生器:產生定幀信號,2bit定幀信號產生的原理和方式需要和OAM模塊合作完成。

數據合成模塊:把28位數據信號和相應的2bit定幀信號合并,成為30bit的幀結構。

發送數據生成模塊:根據camera link 總線的時鐘頻率判定是否對數據進行double處理,處理后的數據為真正的發送數據。

數據加擾模塊:該模塊主要完成加擾過程,保證發送數據中有充足的時鐘信息。

控制模塊:完成對模塊內部各個分模塊的監測和管理,并通過數據處理模塊對內接口模塊和OAM模塊進行相關的數據交流,接受OAM模塊的管理。

時鐘分模塊:為內部各個分模塊提供時鐘。

異常處理模塊:提供不可預測的異常處理,比如復位等,以提高系統的可靠性和穩定性。

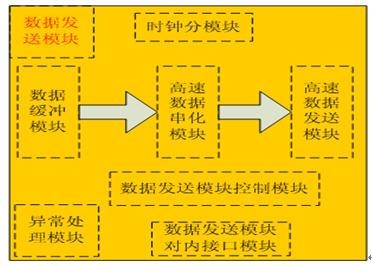

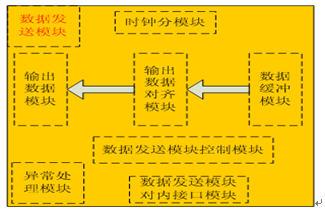

發送單元數據發送模塊

發送單元數據發送模塊完成數據緩沖、高速數據串化和高速數據發送的功能。模塊內部邏輯框圖如圖3.8所示。包括數據緩沖模塊、高速數據串化模塊、高速數據發送模塊、數據發送模塊控制模塊、數據發送模塊對內接口模塊、異常處理模塊、時鐘分模塊

圖3.8 發送單元數據發送模塊內部邏輯框圖

數據緩沖模塊:對來自數據處理模塊產生的數據進行緩沖,提高數據的可靠性和系統的安全性;出現溢出或者空閑的時候上報相關信息給數據發送模塊控制模塊便于OAM。

高速數據串化模塊:用時鐘分模塊提供的高速時鐘(為線路時鐘速率的3倍或者6倍)對數據進行串化,得到原始數據的3倍或者6倍的串行數據流。

控制模塊:接收來自發送單元數據發送模塊的相關信息,通過數據發送模塊對內接口模塊和OAM模塊進行交互,完成OAM模塊對本模塊的管理。

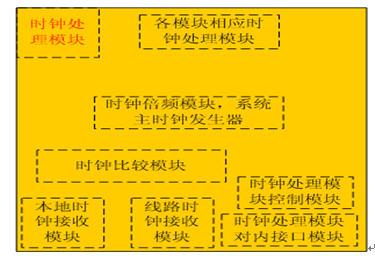

發送單元時鐘處理模塊

發送單元時鐘處理模塊完成FPGA內部時鐘產生和分析。模塊內部邏輯框圖如3.9所示。包括本地時鐘接收模塊、線路時鐘接收模塊、時鐘比較模塊、時鐘倍頻模塊、各模塊相應時鐘處理模塊、控制模塊和對內接口模塊。

圖3.9 發送單元時鐘處理模塊內部邏輯框圖

本地時鐘接收模塊:接收來自本地的時鐘,本時鐘作為OAM 模塊、時鐘處理器控制模塊、并串/串并轉化器控制模塊的工作基準時鐘。以上三個模塊的工作時鐘由三個模塊內部的時鐘分模塊處理得到。

線路時鐘接收模塊:接收來自時鐘處理器的時鐘,本時鐘經處理后作為數據流方向上相關模塊的工作時鐘。

時鐘倍頻模塊,系統主時鐘發生器:產生系統的主工作時鐘,產生重要模塊的工作時鐘。

控制模塊:接收時鐘比較模塊和主時鐘模塊發生器產生的上報信息,對信息進行整理并對這兩個模塊進行相關的自動控制;對需要OAM模塊管理的信息上報到OAM模塊,接受OAM模塊的管理。

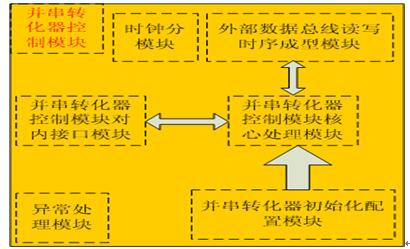

發送單元并串/串并轉化器控制模塊

按照串并/并串轉化器的管理需求,設計并串/串并轉化器的控制管理模塊。本模塊完成并串、串并轉化器的初始化配置,并通過內部接口和OAM模塊進行通信和交流,由OAM模塊進行串并、并串轉化器的設置更改。模塊內部邏輯框圖如圖3.10所示。包括控制器核心處理模塊外部數據總線讀寫時序成型模塊、時鐘分模塊、初始化配置模塊、對內接口模塊 和異常處理模塊。

圖3.10 發送單元并串/串并轉化器控制模塊內部邏輯框圖

以下是各個分模塊的具體介紹。

控制器核心處理模塊:完成對并串、串并轉化器的核心控制工作,包括對轉化器的關鍵數據的監控、關鍵設置的確認等工作,是模塊的核心子模塊。

初始化配置模塊:保存串并、并串轉化器初始化數據,此數據為默認正常工作的數據,不可更改,如果需要更改則上電配置完成后由OAM模塊發起經由核心控制模塊對轉化器進行操作。

異常處理模塊:監測模塊內部的異常信息,上報核心處理模塊的同時進行必要的操作,保證模塊的穩定和安全。

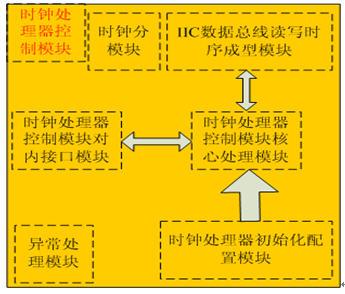

發送單元時鐘處理器控制模塊

按照時鐘處理器的管理需求,設計時鐘處理器的控制管理模塊,本模塊完成時鐘處理器初始化配置,并通過內部接口和OAM模塊進行通信和交流,由OAM模塊進行時鐘處理器的設置更改。模塊內部邏輯框圖如圖3.11所示。包括控制器核心處理模塊、IIC數據總線讀寫時序成型模塊、時鐘分模塊、初始化配置模塊、對內接口模塊、異常處理模塊。

圖3.11 發送單元時鐘處理器控制模塊內部邏輯框圖

控制器核心處理模塊:完成對時鐘處理器的核心控制工作,包括對時鐘處理器的關鍵數據的監控、關鍵設置的確認等工作,是模塊的核心子模塊。

IIC數據總線讀寫時序成型模塊:負責對時鐘處理器的讀寫操作,要求模塊完全滿足IIC數據總線時序的要求,能準確完成讀寫操作,并增加相應的防誤操作功能,確保讀寫的正確性。

初始化配置模塊:保存時鐘處理器初始化數據,此數據為默認正常工作的數據,不可更改,如果需要更改則上電配置完成后由OAM模塊發起,經由核心控制模塊對時鐘處理器進行操作。

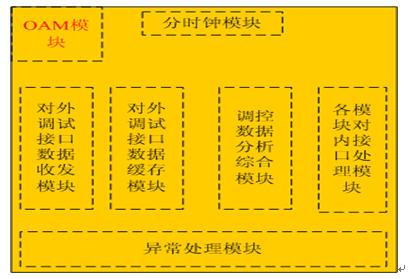

發送單元OAM模塊

本模塊通過內部接口和發送接收模塊其他系統模塊進行通信和交流,對其他模塊進行控制和管理;同時,本模塊通過OAM模塊對外接口模塊和外部的上層管理控制平臺相連,接受外部上層管理控制平臺的指令,完成相應的操作并上報相關的信息,這部分設計還需要進行溝通確認后才能正常開始設計。模塊內部邏輯框圖如圖3.12。包括對外接口數據收發模塊、 對外接口數據緩沖模塊、數據分析綜合模塊、對內接口模塊、時鐘分模塊、異常處理模塊。

圖3.12 發送單元OAM模塊內部邏輯框圖

以下是各個分模塊的具體介紹。

對外接口數據收發模塊:完成串口時序的成型,正確完成串口的讀寫操作,保證讀寫操作的正確性。。

對外接口數據緩沖模塊:緩沖來自串口的信息,在內部處理速度比較慢的情況下仍能保證不丟失指令。

數據分析綜合模塊:對上層管理平臺的命令進行解析,分析命令的動作和需要處理的方式,將復雜命令分解為需要哪幾個模塊完成什么樣的操作,下發給各個實體操作模塊。同時對各個實體模塊上報的信息進行綜合和管理,編制成符合上層管理平臺需要的回復后回復給上層管理控制平臺。

3.3 接收部分單元

圖3.13 接收單元電路模塊整體框圖

接收部分單元完成六路camera link 總線 (兩個 CCD full配置的數據量)的解串工作,先通過波分解復用系統分出每一路camera link 總線的數據,然后再把每一路串化的camera link 數據解串,恢復成標準的并行信號。圖3.13是接收單元整體功能框圖:

接收單元包含如下幾個模塊,如圖3.14:

接收單元數據接收模塊:完成正確接收來自serdes的數據的功能;

接收單元數據處理模塊:完成數據的核心處理功能;

接收單元數據發送模塊:完成正確將分析出來的數據發送到Camera link協議轉化器的功能;

接收單元串并轉化器控制模塊:完成對串并轉化器的OAM功能;

接收單元時鐘處理模塊:實用內部的時鐘部件完成時鐘的相應處理,比如分頻、倍頻、相位調整等;

接收單元時鐘處理器控制模塊:完成對時鐘處理器的OAM的功能;

接收單元OAM模塊:和上層控制管理器的配合,完成發送系統的OAM工作。

圖3.14 接收單元模塊劃分

下面詳細介紹接收部分單元模塊具體功能及實現:

接收單元數據發送模塊

接收單元數據發送模塊完成數據的緩沖、對齊處理并發送給camera link 協議轉化器的功能。模塊內部邏輯框圖如圖3.15。包括數據緩沖模塊、數據對齊模塊、輸出數據模塊、數據發送模塊控制模塊、數據發送模塊對內接口模塊、異常處理模塊和時鐘分模塊

圖3.15接收單元數據發送模塊內部邏輯框圖

數據緩沖模塊:對發送單元數據處理模塊產生的數據進行緩沖,提高數據的可靠性和系統的安全性;出現溢出或者空閑的時候上報相關信息給數據發送模塊控制模塊便于OAM。

數據對齊模塊:對數據進行對齊操作,并進行相關的處理,保證發送出去的數據滿足camera link 的規范要求。

輸出數據模塊:進行時序調整,將數據發送到camera link 協議轉化器。

控制模塊:接收來自接收單元數據發送模塊的相關信息,通過數據發送模塊對內接口模塊和OAM模塊進行交互,完成OAM模塊對本模塊的管理。

對內接口模塊:完成數據發送模塊控制模塊和接收單元OAM模塊之間的通信和數據交流。

異常處理模塊:提供不可預測的異常處理,比如復位等,以提高系統的可靠性和穩定性。

時鐘分模塊:提供本模塊需要的時鐘。

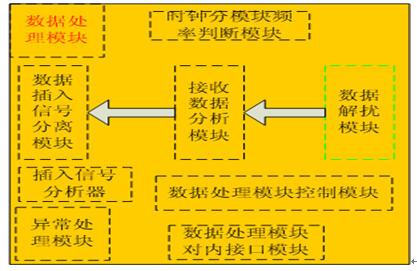

接收單元數據處理模塊

接收單元數據處理模塊完成核心的數據接收的功能。模塊內部邏輯框圖如圖3.16所示。包括數據解擾模塊、數據分析模塊、數據插入信號分離模塊、插入信號分析器、數據處理模塊控制模塊、數據處理模塊對內接口模塊、時鐘分模塊、異常處理模塊。

圖3.16接收單元數據處理模塊內部邏輯框圖

以下是各個分模塊的具體介紹。

數據解擾模塊:該模塊主要完成解擾過程,保證正確提取數據。

數據分析模塊:完成30bit的幀結構的定幀操作,并正確確定出28bit數據信號和相應的定幀信號,并判定數據是否經過double處理。工作狀態可以由數據處理模塊控制模塊進行相關的設置和監測。

數據插入信號分離模塊:正確分離出數據和插入信號。根據是否對數據進行double處理判定camera link 總線的時鐘頻率,處理后的數據為真正的接收數據。

插入信號分析器:分析對端插入的數據,提取相關的信息,并上報到控制模塊。

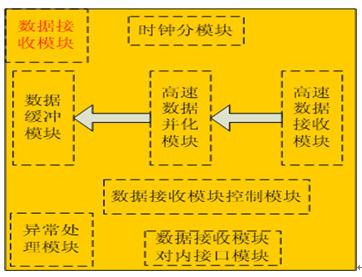

接收單元數據接收模塊

接收模塊數據接收模塊完成串行數據高速接收、高速串化數據的并化處理、數據緩沖的功能。模塊內部邏輯框圖如圖3.17所示。包括高速數據接收模塊、高速數據并化模塊、數據緩沖模塊、數據接收模塊控制模塊、數據接收模塊對內接口模塊、異常處理模塊和時鐘分模塊。

圖3.17接收單元數據接收模塊內部邏輯框圖

以下是各個分模塊的具體介紹。

高速數據接收模塊:以和Serdes 相匹配的形式接收來自serdes的高速數據。

高速數據并化模塊:完成高速數據的串并轉化功能。

數據緩沖模塊:對接收數據進行緩沖,提高數據的可靠性和系統的安全性。出現溢出或者空閑的時候上報相關信息給數據接收模塊控制模塊便于OAM。

接收單元時鐘處理模塊

接收單元時鐘處理模塊和發送單元采用相同的方案。可參見發送單元。

接收單元并串/串并轉化器控制模塊

接收單元并串/串并轉化器控制模塊和發送單元采用相同的方案。可參見發送單元。

接收單元時鐘處理器控制模塊

接收單元時鐘處理器控制模塊和發送單元采用相同的方案。可參見發送單元。

接收單元OAM模塊

接收單元OAM模塊和發送單元采用相同的方案。可參見發送單元。

3.4 發送、接收單元并串/串并轉化器模塊

根據系統的設計需求,可以用一款通用串行器及解串器組成高速并串、串并模塊。串行/解串器芯片組數據串行速度最高速度應高于Camera link的最高的2.38Gbps速率,以保證CCD在最高速率下可以使用;串行/解串器芯片組數據串行速度下限應低于Camera link的最低的560Mbps速率,以保證CCD在最低速率下可以使用。并且解串器不需要本地的時鐘,完全在串行碼流中提取時鐘。通常芯片在滿足最高速度要求的情況下,在滿足最低速率需求方面存在問題,無法滿足camera link 的最低560Mbps的要求,則需要對速率較低的camera link 數據進行倍速調整,以達到串化/解串芯片組能夠支持的速率,這也是該系統設計中設計難點之一。

3.5 OAM接口模塊

OAM接口模塊采用422/232兼容的接口模塊,設計相對簡單。OAM模塊具體的功能設計已經在之前核心模塊中有詳細描述,這里不贅述。

四、發送板及接收板實物圖

圖4.1 發送板實物圖

圖4.2 接收板實物圖

評論