四通道高速數據采集系統設計

摘要:為滿足合成孔徑雷達中對寬帶I.Q基帶信號數據采集存儲的迫切需求,介紹了一種基于高速AD器件,以大容量FPGA為核心的高速數據采集系統設計方法。利用高速ADC器件實現對寬帶I,Q信號采樣,FPGA完成AD的參數配置、高速數據緩存及各種時序控制,實現了四通道500M SPS的高速數據同步采集與傳輸。測試結果顯示:系統動態范圍大,信噪比高。系統為標準6U插件,電路實現簡單、使用靈活,已成功應用于多個雷達系統中完成各項實驗。

關鍵詞:高速數據采集;高速ADC;FPGA;高速PCB

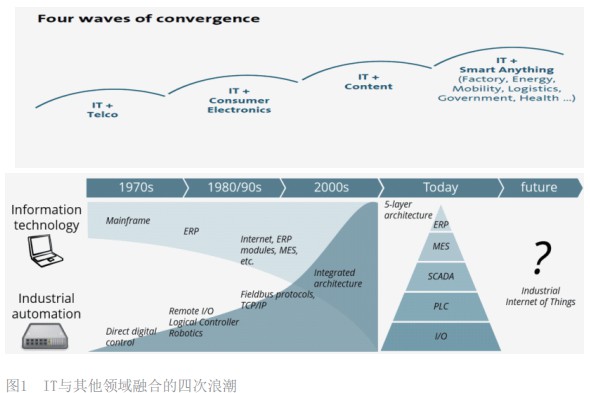

合成孔徑雷達(Synthetic Aperture Radar,SAR)是一種高分辨率微波成像雷達,可以全天候、全天時地利用微波照射獲得地面目標的散射信息,是獲得地面信息的重要手段。它通過脈沖壓縮提高距離分辨率,采用合成孔徑技術提高方位向分辨率,分辨率的大小取決于信號帶寬和回波多普勒帶寬。提高分辨率是機載SAR的發展方向。SAR發射信號的帶寬一般在幾百兆,根據奈奎斯特采樣定理,要求ADC的采樣率最小兩倍于輸入信號的頻率,因此高速數據采集技術越來越引起人們的關注。

1 高速數據采集系統設計方案

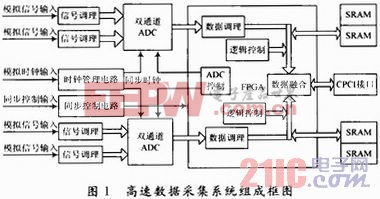

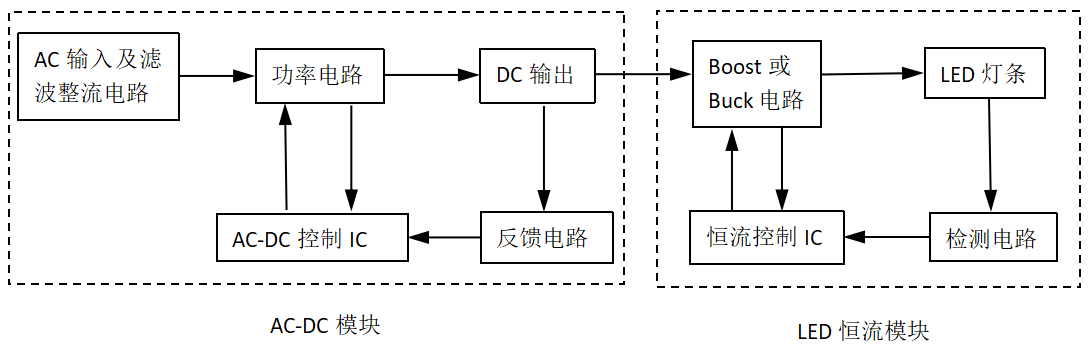

本系統從完成的功能方面來劃分共包括數據采集和數據融合兩部分;數據采集主要完成將經接收通道接收、放大、濾波并正交解調后的雷達回波信息進行模數變換和存貯;數據融合主要完成多路數據采集后數據的融合,并為接收回波信號的數字傳輸提供合適的接口,并將數據以要求的數據率和格式傳輸給后續信號處理系統。本采集系統為標準的6U插件,電路主要組成包括模擬信號調理電路、高速ADC、高速時鐘管理電路、大容量數據緩存、系統時序控制電路、CPCI接口電路等,可實現四通道500 MSPS的高速數據采集,實現框圖如圖1所示。

1.1 核心器件ADC的選擇

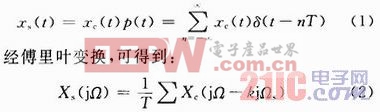

奈奎斯特采樣定理指出:當采樣頻率Ωs>2Ωm(Ωm為輸入信號的最高頻率)時,采樣后的信號可惟一地恢復原模擬信號。給定一個連續時間信號xc(t),采樣后的離散時間信號xs可表示為原信號與一個周期脈沖串p(t)的乘積,如式(1)所示,其中T為采樣周期。

式中:Ωs=2 π/T,為采樣頻率。設xc(t)為一個帶限信號,帶寬為ΩN,當|Ω|>ΩN時,Xc(jΩ)=0,由式(2)可見,xc(t)經采樣后的頻譜Xs(jΩ)就是將Xc(jΩ)在頻率軸上搬移到0,±Ωs,±2Ωs,…,±nΩs處。因此,唯有當Ωs>2ΩN時,頻譜不會發生混疊。

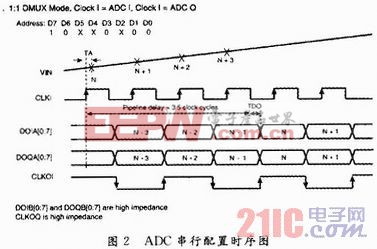

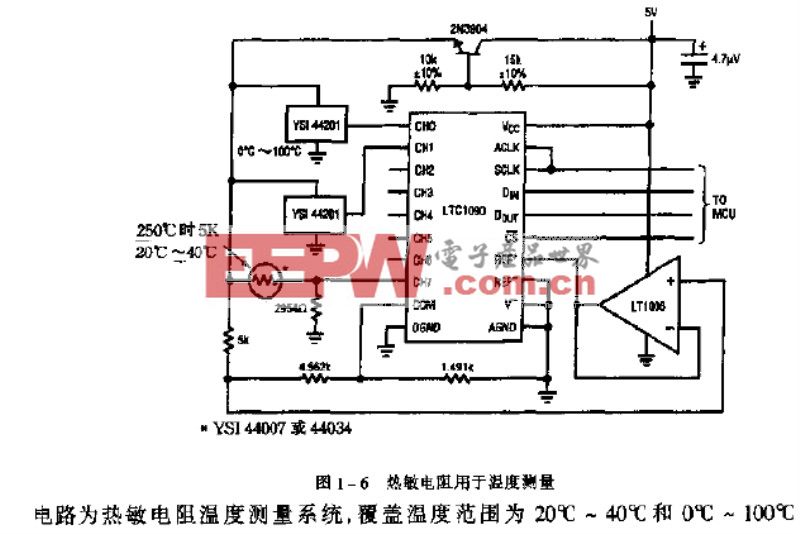

雷達系統要求中頻輸入信號為0~200 MHz,根據上述分析,ADC的采樣時鐘必須大于400 MHz,因此本電路選用一款低功耗雙通道高速ADC芯片,每個通道最高采樣率為500 MSPS,在交錯模式下雙路并行采樣可實現最高1 GSPS的采樣,具有8 b轉換精度,此芯片內部集成了1:1和1:2的數據多路分配器,并提供了LVDS電平的低電壓差分信號輸出,可以降低數據輸出率,并且ADC輸出數據可以和多種FPGA直接互聯,從而節省硬件資源。此款ADC芯片的所有參數設置均可通過三線串行方式實現,在設計中,利用FPGA編程實現串行配置的工作時序,從而控制ADC的工作模式。串行配置時序圖如圖2所示。

1.2 其他核心器件的選擇

FPGA選用Altera公司StratixⅡ系列芯片,此器件支持多種電壓接口,通過軟件對管腳電平設置可以與多種邏輯電平直接接口,36 384個ALMs,192個18 b×18 b的乘法器,408個M4K RAM,488個M512RAM,由于系統需要四片片外RAM進行數據緩存,采用兩片FPGA可滿足邏輯控制要求和數據緩存要求。

在高速數據采集系統中,時鐘電路是整個系統的最關鍵部件。采樣時鐘的抖動和相位噪聲會完整地傳遞給采樣輸出,從而影響系統的信噪比。本系統的采樣時鐘由外部時鐘源提供,為ECL電平,因此只需要對輸入時鐘源進行電平轉換及電路匹配設計,以達到ADC的時鐘輸入要求,選用Semiconductor公司的MC100系列芯片對時鐘電路進行管理,此系列芯片傳輸延時220 ps,周期間抖動0.2 ps,可滿足時鐘分配及傳輸要求。

1.3 高速數字信號處理與多通道數據同步

系統所選ADC輸出為LVDS電平模式,LVDS是低電壓的差分信號,功耗低,噪聲小,可以有效地降低對ADC模擬通道的數字干擾;每個通道的數據輸出可采取1:1或1:2的降速輸出,由于所選FPGA的LVDS信號輸入范圍是300~1 250 Mb/s,所以采用1:1的數據輸出格式,在FGPA中編程對ADC進行三線串行配置來實現。FPGA自帶IP核(ALTLVDS)可實現接收ADC的LVDS數據降速轉換,數據的緩存及傳輸等邏輯控制功能均在FPGA中運用Verilog硬件語言來完成。

對于多通道高速數據采集,通道之間數據同步傳輸是保證后續信號處理正確實現的前提。本系統通過對采樣時刻的同步和輸出時序的同步設計來實現。采樣時刻的同步即保證每個通道采樣時鐘的一致,在電路設計時,采用單路時鐘輸入,然后通過同步時鐘管理電路將采樣時鐘分配給每一個通道,并保證路徑等長;時序一致性包括:一方面,每個通道ADC的三線串行配置通過嚴格的同步時序來控制;另一方面,每個通道都以同一個脈沖觸發信號的上升沿或下降沿為起始標志進行數據緩存和傳輸。此觸發信號和工作時鐘完全同步,作為整個系統的同步信號。這樣就保證了各個通道之間數據傳輸的同步。

評論