多通道數據采集系統設計

摘要 介紹了一種基于FPGA+DSP的多路數據采集系統的設計方案,描述了系統的硬件設計方案和硬件電路,闡述了信息采集過程以及外圍通訊接口及軟件設計。通過Quartus II8.0及CCS 2進行系統仿真,證明了系統設計方案的可行性。

關鍵詞 數據采集系統;FPGA;DSP;FIFO

在以往數據采集系統中,單片機、DSP常被選作主控制器,但隨著FPGA性能的不斷提高,具有時鐘域高、內部延時小、速度快、全部邏輯南硬件完成等優點,因此在高速數據采集方面FPGA有著較大優勢,但也存在難于實現復雜算法的缺點。而DSP適合于高速算法的處理,系統采用FPCA+DSP方案,彌補了系統的不足。系統數據采集的控制、緩存及外圍通訊部分,用FPCA硬件實現。算法處理由DSP完成。在線采集的數據存放在DSP外掛的SRAM中。

設計采用DE2、THDB-ADA平臺進行開發。DE2平臺選用FPGA EP2C35F672。THDB-ADA是針對DE2開發板設計的一款子開發板,由FPGA實現對A/D的控制。在系統中只用到了模塊的A/D轉換部分。其中芯片AD9248是一款雙通道模數轉換器。另外DSP選用TI推出的TMS320UC5402。

1 系統設計

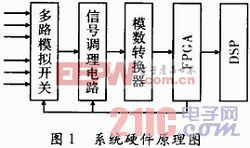

數據采集系統硬件原理如圖1所示,由圖1知DSP收到上位機發送的命令完成系統工作參數的配置,然后向FPGA發送指令,FPGA收到指令后一是對多路模擬開關進行選通讓選通信號通過信號調理電路實現電平調整,并進行A/D轉換的時序控制,二是把轉換好的數據進行數據緩存,當FIFO滿時并產生DSP能識別的外部中斷信號及標識信號,通知DSP采集數據,最后DSP對采集到的數據進行濾波處理、變換、譜分析。

2 硬件設計

2.1 通道切換電路

系統采用16通道ADG506模擬開關進行各通道的切換。并具有開關速度快、泄漏小等特點。主要有A0~A3,S1~S8,D,EN端口。其中A0~A3是二進制地址信號輸入端,譯碼結果用于選擇有效的輸出通道;S1~S16是16路信號的輸入端,在此可根據需要選擇通道數。D是被選擇通道的信號輸出端;EN是選擇開關使能控制端高電平為有效。FPGA通過數據幀來進行通道選擇,每次只選擇一路,經A/D轉換后送入FIFO。

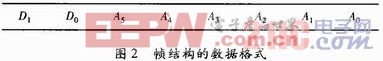

圖中,A0~A5表示所選擇通道,其中A4,A5恒為0。D0~D1表示幀結構數據起止標識位。

2.2 信號調理電路

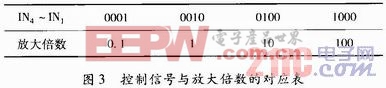

信號調理電路對模擬信號進行一定的放大/衰減,使信號的幅度滿足A/D芯片要求。前向調理電路采用高速低噪聲的模擬開關MAX4545去選擇不同的反饋電阻,同模擬運算放大器MAX817構成標準的反相運算放大器來實現前向調理。MAX817的單位增益3 dB,截止頻率高達50 MHz,滿足帶寬的要求。MAX4545的4根控制線由FPGA設計控制電路去控制,具體是由復位按鈕進行邊沿觸發,使4位輸出電平在0001,0010,0100,1000之間輪流切換,將輸出電平去控制MAX4545的4根控制線,這就實現了不同的放大倍數之間切換,控制信號與放大倍數的對應關系,如圖3所示。

2.3 濾波電路

系統接收到的模擬信號總是混有噪聲成分,為達到奈奎斯特采樣定理所要求信號的頻率范圍,需要利用低通濾波器除去干擾信號及抑制混疊現象,即進行衰減與濾除。設計選用二階巴特沃斯低通濾波電路來濾除信號中的高頻分量,其特點是通頻帶內的響應曲線最大限度平坦,無起伏,而在阻頻帶逐漸衰減為0.2階的巴特沃斯低通濾波器幅頻。

2.4 FPGA硬件電路設計

FPGA作為接口電路主芯片,充當DSP的前端接口元件,將各種信號轉換為DSP能讀取的并行格式數據。

FPGA的開發采用自頂向下的設計方法,即指將一個系統按功能劃分為不同的模塊,而模塊再根據需要劃分為二級模塊,依此直到模塊易被實現為止。通過Verilog編程FPGA即可生成雙口SRAM模塊、ADC接口模塊、調理電路放大倍數控制模塊、數據接收模塊等,以實現對輸入信號的采集、存儲、處理和輸出。

評論