基于AD7762和FPGA的數據采集系統設計

摘要 為了滿足音頻數據采集過程中對頻率和分辨率等技術指標的要求,設計了一種高速數據采集裝置。文中設計采用Altera公司的Cvclone系列FPGA芯片EP1C4F400在QuartusⅡ環境下使用Verilog語言控制ADI公司的AD7762A/D轉換器實現數據采集。通過串口將數據傳給上位機,完成數據分析和顯示功能FPGA控制整個系統的采集時序。

關鍵詞 數據采集;AD7762;FPGA;寄存器控制;串口

隨著通信技術的發展,通信業務不斷擴大,人們越來越重視高速數據采集和處理技術。數據采集系統主要包括增益放大器、A/D模數轉換器、功能控制端。文中設計了一種以FPGA為控制核心,用于控制A/D的轉換時序及數據傳輸的高速數據采集系統。

1 系統總體結構

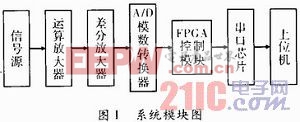

設計系統以FPGA芯片EP1C4F400作為采集系統的核心控制單元,采用模數轉換芯片AD7762作為數據采集的核心模塊。由A/D轉換后產生的數字信號通過串口傳輸到上位機,由上位機對數據進行一系列分析。該系統主要南前端處理模塊、A/D轉換控制模塊、FIFO緩存模塊及串口模塊組成,系統如圖1所示。

2 硬件設計

2.1 模數轉換模塊AD7762

AD7762是ADI公司近年推出的一款高性能、低功耗、并行24位Sigma-Delta模數轉換芯片ADC。寬輸入帶寬,在625 khit·s-1時信噪比為106 dB的高速Sigma-Delta轉換,使得其能夠高速獲得數據。片上集成用于信號緩沖的差分放大器,低通數字FIR數字濾波器,需要最少的外圍設備。另外,AD7762還提供了可編程的采樣速率和可調整的FIR數字濾波。AD7762要求在無復雜的前后端信號處理設計中有較高的SNR。

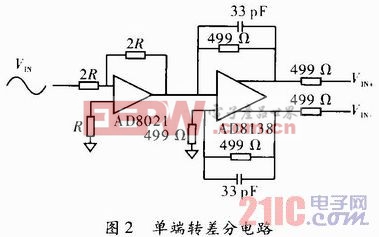

在應用正常模式下,為實現指定性能,差分放大器需要被配置為前端平滑濾波器,前端使用低噪聲,高性能的運算放大器對其進行配置,實現單端信號轉差分號,然后驅動AD7762。運算放大器使AD8021,差分放大器使用AD8138。信號由AD8021運算放大器輸入端口接入,根據A/D輸人信號的幅度標準進行輸入信號幅度的調整,經由AD8138差分放大器進行單端轉差分處理,之后送入模數轉換器中。其電路實現如圖2所示。

AD7762有許多用戶可編程寄存器。控制寄存器用于設置濾波頻率、濾波器配置、時鐘分頻器等。AD7762使用16位雙向并行接口,該接口受控于![]() 。

。

2.2 主控制FPGA模塊EP1C4F400

系統的主控制器采用Altera公司Cyclone系列的EP1C4F400C8N。Ahera Cyclone系列FPGA從根本上針對低成本進行設計,具有專業應用特性。器件基于成本優化的全銅1.5VSRAM工藝,輸入輸出電源電壓是3.3 V。內核供應電壓是1.425~1.575 V。Cyclone FPGA綜合考慮了邏輯、存儲器、鎖相環(PLL)和高級I/O接口。具有專用外部存儲器接口電路,支持DDRFCRAM和SDRAM器件以及SDR SDRAM存儲器的連接。支持單端I/O標準如3.3 V、2.5 V、1.8 V、LVTTL、LVCMOS、PCI、和SSTL-2/3,滿足當前系統需要。通過LVDS和RSDS標準提供多達129個通道的差分I/O技術支持,每個LVDS通道信號數據率高達640 Mb·s-1。FPGA中有兩個鎖相環(PLLs),提供6個輸出和層次時鐘結構,以及復雜設計的時鐘管理電路。FPCA中包括17個M4K存儲塊。每塊提供288 kbit的存儲容量,能夠使配置支持多種操作模式,包括RAM、ROM、FIFO及單口和雙口模式。

2.3 系統后端數據傳輸模塊

在數據傳輸模塊中,設計調用FPGA片上資源實現FIFO緩存。存儲深度為256×16 bit。由于A/D的采樣頻率和串口的讀寫頻率不同,因此設計中采用讀寫時鐘異步的FIFO。FIFO中的數據通過串口傳輸到上位機,設計中串口芯片采用美信公司專門為RS-232標準串口設計的單電源電平轉換芯片MAX3232芯片,使用+3.3 V單電源供電。

3 軟件設計

系統利用Ahera QuartusⅡ軟件完成FPGA程序的編寫。Altera QuartusⅡ軟件提供完整的多平臺設計環境,能夠直接滿足特定的設計需要,為FPGA開發提供全面的設計環境。QuartusⅡ開發軟件支持多種設計輸入方式。由于FPGA支持Verilog/VHDL混合開發,設計主要采用文本形式文件輸入方式和存儲器數據文件出入方式,采用的Verilog/VHDL硬件描述語言設計輸入,易于實現自頂向下的設計方法,易于模塊劃分和復用、移植性好、通用性強,具有較好的硬件平臺無關性,設計不因芯片工藝和結構的改變而改變,利于向ASIC移植。

3.1 A/D轉換器的控制寄存器

A/D時序分為寫時序和讀時序。寫時序控制A/D寄存器的寫操作。寫操作包括兩部分,先寫控制寄存器2,給A/D加電,控制寄存器2的地址是0X0002,高10位全部是0。低6位的內容如圖3所示。

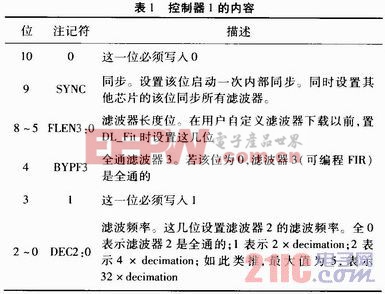

![]() 設置A/D的時鐘分頻比率,CDIV=1,則ICLK=MCLK。CDIV=0,則ICLK=MCLK/2。設計硬件電路中連接的時鐘是MCLK=40 MHz,但A/D中允許的最大的ICLK時鐘是20 MHz,需要對外部時鐘進行分頻,因此此位設為0。D1PD位置高將關斷片上差分放大器,本設計中置0,第二位寫入1。再寫控制寄存器1,設置A/D的濾波頻率、濾波器長度位、數據輸出頻率等。控制器1的內容如表1所示。

設置A/D的時鐘分頻比率,CDIV=1,則ICLK=MCLK。CDIV=0,則ICLK=MCLK/2。設計硬件電路中連接的時鐘是MCLK=40 MHz,但A/D中允許的最大的ICLK時鐘是20 MHz,需要對外部時鐘進行分頻,因此此位設為0。D1PD位置高將關斷片上差分放大器,本設計中置0,第二位寫入1。再寫控制寄存器1,設置A/D的濾波頻率、濾波器長度位、數據輸出頻率等。控制器1的內容如表1所示。

評論