基于Matlab/DSP Builder多波形信號發生器的設計

1 引言

本文引用地址:http://www.j9360.com/article/192136.htm傳統的波形發生器多采用模擬分立元件實現,產生的波形種類要受到電路硬件的限制,體積大,靈活性和穩定性也相對較差。采用FPGA器件直接實現多種波形信號發生器,配以相應的外圍器件實現的波形發生器具有設計簡單、外圍電路少、頻率穩定性高、可靠性高、輸出波形穩定、現場可編程等優點,因而在現代電子設計中,常常采用FPGA器件來實現多種波形信號發生器,利用FPGA實現多種波形信號發生器的方法也很多,但其設計方法均過于復雜,要求設計人員對VHDL 語言要相當熟悉,才能編寫相應的程序。采用Matlab/DSP Builder建立模型來實現多種波形信號發生器,其設計簡單,不需要編程,也能根據需要設計出相應的多波信號發生器[1][2][4][6]。

2、多波信號發生器的數學模型

2.1 鋸齒波的產生

在Matlab/Simulink下,有一模塊名叫Increment Decrement模塊,由于Increment Decrement模塊隨著時間的變化而不斷的從0計數到255 ,到了255后清0,接著又從0開始計數這樣周期性的產生鋸齒波。

2.2 正弦波的產生

利用Increment Decrement不斷計數,根據計數找到查找表的地址取出里面的值,正弦函數的調用格式為Sin(【起始值:步進值:結束值】),該模塊為一個輸入為6位輸出值為8位的正弦查找表模塊。

2.3 方波的產生

由于產生的正弦波的值從0到255,我們可以使用一個比較器進行比較,根據比較值的大小產生占空比不同的方波,此處我們設置一個值為127的常數,當輸出正弦波的值大于等于127的時候比較器的值為1,反之為0。比較器輸出的值可以進行放大,比如放大127倍。這樣即可生成方波。

2.4 三角波的產生

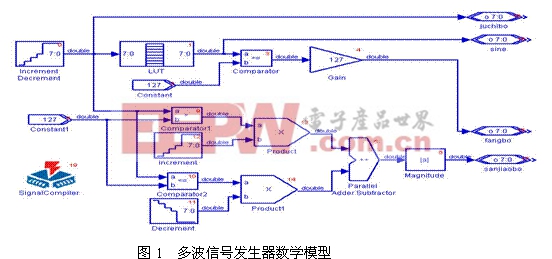

同理利用比較器的性質跟Increment Decrement模塊輸出的值進行比較,當Increment Decrement模塊輸出的值小于等于127時比較器模塊10為1,然后再與Increment模塊相乘,相乘的結果為127到0;當 Increment Decrement模塊輸出的值大于127時比較器模塊9為0,與Increment模塊相乘,相乘的結果為0到127;以上兩者進行相加后在經過一個絕對值變化器,就可以產生的很好的波形。根據以上分析其建立的模型如圖1所示[5]。

3、用ModelSim進行RTL級的VHDL仿真

3.1 多波信號發生器的模型文件MDL轉換成VHDL

在Simulink中完成仿真驗證后,就需要把設計轉到硬件上加以實現。這是整個DSP Builder設計流程中最為關鍵的一步,在這一步,可以獲得針對特定FPGA芯片的VHDL代碼。雙擊多波信號發生器數學模型中的 SignalCompiler模塊,然后再在彈出的對話框中分別點擊“Convert MDL to VHDL”、“Synthesis”和“Quartus II”,這樣就可以把多波信號發生器的數學模型文件轉換成特定的VHDL代碼。

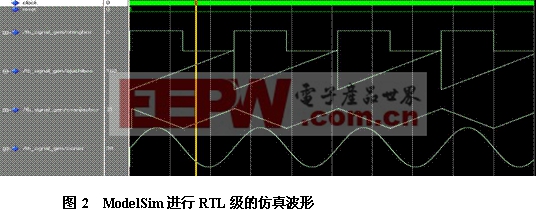

3.2 用ModelSim進行RTL級的VHDL仿真

評論