無線傳感器網絡SOC芯片的低功耗設計 (1)

在系統層次上,RISC CPU核設計了空閑模式及停止模式,來節省功耗。RISC CPU核進入空閑模式或停止模式時,CPU內部時鐘停止運行,同時內部寄存器保持數據。

4. 結構層次上的低功耗設計

通過仔細分析整個SOC芯片的功耗來源,可知RISC CPU核,RAM,Flash及基帶處理模塊占去了絕大部分。下面從結構層次進行低功耗設計。

4.1 RISC CPU核的低功耗設計

微處理器的功耗降低可以通過降低頻率,及降低工作電壓的方法來解決。在網絡節點SOC結構層次上的設計中,除了采用慢速時鐘,及低電壓供電的方法,還同時針對數據路徑進行優化,主要目的是為了減少電路中不必要的翻轉。指令譯碼數據路徑的優化:一般情況下,CPU中所有的執行單元直接接在指令譯碼單元后面。一旦有新的譯碼數據輸入,與其相連的所有執行單元電路也去進行翻轉,造成不必要的功耗浪費。所以,在不影響時序功能的情況,設計分離的內部總線,將不執行的單元輸入數據及控制信號鎖存,其輸入信號保持不變,動態功耗可以減少。芯片內部集成了RAM及Flash ROM。為了降低這兩者的功耗,避免不必要的翻轉,內部總線與RAM,Flash 的接口單元設計鎖存器,這樣的話,只有CPU訪問相應的地址時,RAM及Flash內部才進行翻轉。

4.2基帶處理模塊的低功耗設計

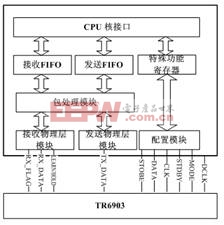

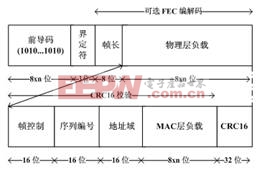

基帶處理模塊的設計框圖如圖 2所示;其基于IEEE 802.15.4協議的物理層幀及數據鏈路層幀結構如圖 3所示。從提高cpu的效率和減少功耗角度出發,基帶處理模塊采用中斷方式與CPU通線。基帶處理模塊發送完接收FIFO的數據幀,向CPU申請發送中斷,等待CPU寫入新的數據到發送FIFO;當基帶處理模塊接收到TR6903模塊發來的數據幀,存放入接收FIFO中,產生接收中斷等待CPU處理。

圖 2 基帶處理模塊結構框圖

圖 3 物理層及數據鏈路層幀結構

基帶處理模塊主要采用并行結構與流水線技術來降低功耗。發送功能與接收功能的物理層發送模塊,緩沖區都是并行結構。配置模塊也是分開來設計,數據的處理方式也是并行。包處理模塊的中CRC16也是采用并行結構進行校驗的。這樣設計的好處,是為了在慢時鐘頻率下,通過并行設計提高性能,達到與高速時速一樣的性能。在圖 2中的各子模塊與子模塊之間都有流水級,也就是鎖存器,不僅僅為了減少不必要的翻轉,更重要的減少關鍵路徑上的長度,從而達到間接降低功耗的目的。

基帶處理模塊低功耗結構設計如下:

評論