基于DSP和FPGA技術的低信噪比雷達信號檢測

摘要:提出一種基于DSP和FPGA技術的低信噪比情況下雷達信號檢測技術的工作原理與硬件實現方法,采用數字化的處理方法處理信息,取代傳統使用的模擬檢測技術,并對實現的檢測方法和關鍵算法做了詳細介紹。

關鍵詞:高速A/D;DSP;FPGA;低信噪比

我國目前的海事雷達大多為進口雷達,有效探測距離小,在信噪比降為3 dB時已經無法識別信號。隨著微電子技術的迅猛發展,高速A/D(模擬/數字轉換)和高速數字信號處理器件(Digital Signal Proeessors,DSP)、高速現場可編程邏輯器件(Field ProgrammableGate Array,FPGA)的出現,可以在不增加現有雷達發射功率和接收靈敏度的前提下,在信噪比降為3 dB時能測到雷達信號,使雷達的有效作用距離提高。本文主要介紹基于DSP和FPGA技術的低信噪比情況下雷達信號的檢測。

1 設計思想

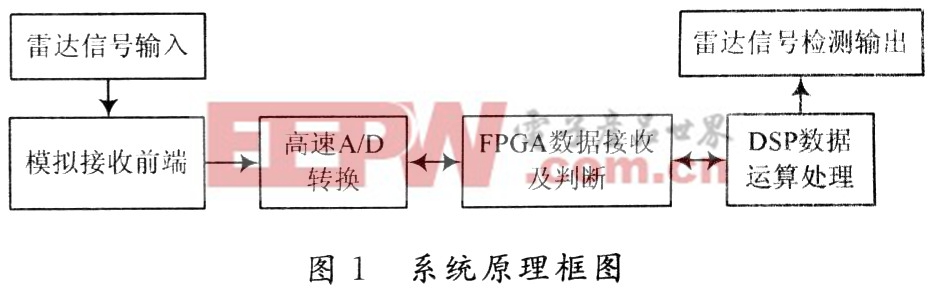

本技術的設計思想主要是通過對接收到的雷達信號進行高速A/D采樣,然后利用DSP和FPGA芯片對采樣后的信號幅度和輪廓進行判斷,以實現低信噪比條件下雷達信號的識別,從而還原出有效信號。系統原理框圖如圖1所示。

2 系統的硬件設計

2.1 高速A/D設計

大部分雷達信號為射頻脈沖信號,常用的工作頻率范圍為2~18 GHz,脈沖持續時間在幾十納秒到幾百微秒。假設檢測信號脈寬為150 ns,根據奈奎斯特采樣原理,必須選用高速的A/D轉換器才不使信號丟失,實際實現需盡可能地多采樣數據,才有利于信號幅度和輪廓的識別。經綜合考慮,決定每隔8 ns采樣一個數據,150 ns可采樣18個數據,選用125 MHz的高速A/D轉換芯片MAX19541,數據采樣位數為12位。MAX19541經過優化,在高于300 MHz的高IF頻率時具有優異的動態性能。MAX19541采用1.8 V單電源工作,轉換速率高達125 MSPS,功耗僅為861 mW,差分模擬輸入可以是交流或直流耦合。該器件還具有可選的片上2分頻時鐘電路,允許高達250 MHz的時鐘頻率。這有助于降低輸入時鐘源的相位噪聲,從而獲得較高的動態性能,同時采用差分的LVPECL采樣時鐘,可以獲得最佳性能。MAX19541數字輸出為CMOS兼容,數據格式可選擇2的補碼或偏移二進制碼,可工作在并行模式,以采樣速率從單個并行端口輸出數據;或工作在demux并行模式,以1/2采樣速率從兩個單獨的并行端口輸出數據。MAX19541的這些優異性能不僅滿足高速采樣的要求,并且外圍器件少,與后級芯片接口簡單,無需電平轉換。

2.2 FPGA設計

FPGA芯片主要實現數據緩存和電平判斷功能,其核心問題為基于用雙端口塊存儲器(Block RAM)的FIFO模塊設計和電平判斷檢測設計。

由于接收機設計的目的是準確實時地處理輸入數據,高速A/D的輸出必須由高速數字電路處理,否則數字化后的數據就會丟失,或者系統只能工作在非實時模式,所以這些處理方法的計算速度則是目前最為關心的問題。為了能夠及時處理高速采樣(8 ns)數據,不丟失數據,后繼數字處理器件FPGA處理芯片必須選用工作速度高于8 ns的芯片,這里選用了Xilinx公司的SPARTAN XC3S200。Spartan-3 FPGA采用90 nm技術,I/O管腳都支持全SelectIO-Ultra功能,實現了快速、靈活的電接口,足夠多的I/O管腳可分別與前級的12位高速A/D轉換芯片、后級的DSP處理器相連。該器件具有SRL16移位寄存器邏輯和分布式存儲器,能夠滿足高速大容量的數據緩存和判斷處理的需求。FPGA芯片的數據緩存功能基于用雙端口塊存儲器(Block RAM)的FIFO模塊設計,容量為負責存儲高速A/D轉換器轉換過來的并行12位數據,供DSP進行數據處理。系統的工作時鐘是65 MHz,在實現該模塊時,調用COREGenerator來生成FIFO,通過FPGA中的專用雙端口塊存儲器資源,生成的FIFO模塊,其存取速度可以達到100 MHz以上,完全滿足實際使用的需求。

FPGA芯片的電平判斷檢測功能在后面的FPGA檢測方法中有詳細說明。

2.3 DSP設計

DSP處理器負責電平判決門限的運算處理,選用TI公司的TMS320F2812芯片。TMS320F2812提供了強大的計算能力,最高運行速度可達150 MIPS,具有處理性能更強,外設集成度更高,程序存儲器更大等特點。TMS320F2812包含了多種芯片,可提供不同容量存儲器和不同外設,以滿足各種應用的要求。TMS320F2812芯片通過外部地址與數據總線與FP-GA處理芯片相連接。DSP處理器不斷從FPGA芯片的FIFO中讀出A/D轉換后的雷達接收數據,經過運算處理得出噪聲的均方根值,再計算出雷達信號的判決門限值寫入FPGA芯片的電平接收寄存器中,以進行有用信號的判斷處理。

評論