基于FPGA的多通道HDLC收發電路設計

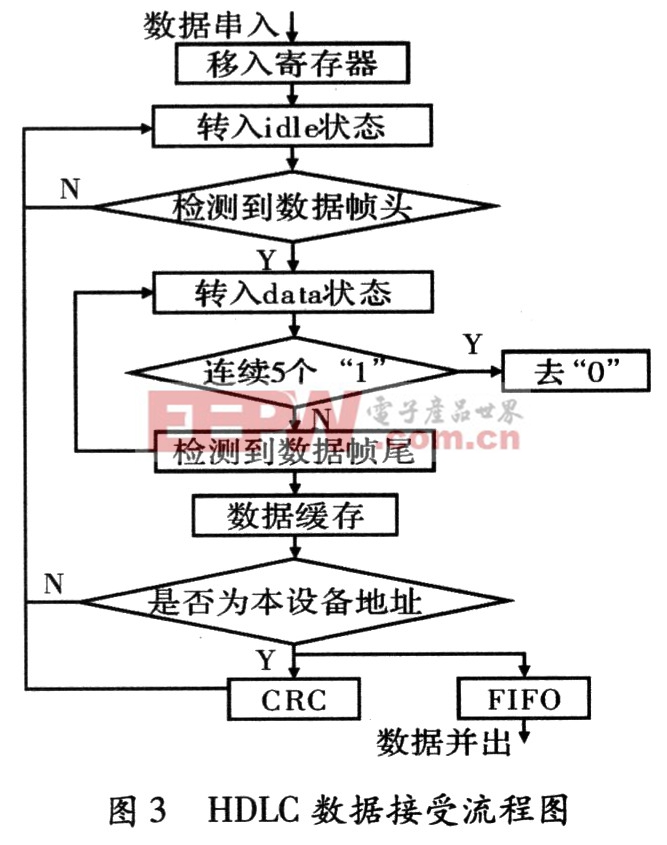

目的地址不是本設備的數據幀將被拋棄,流程圖如圖3所示。

3 實驗結果和分析

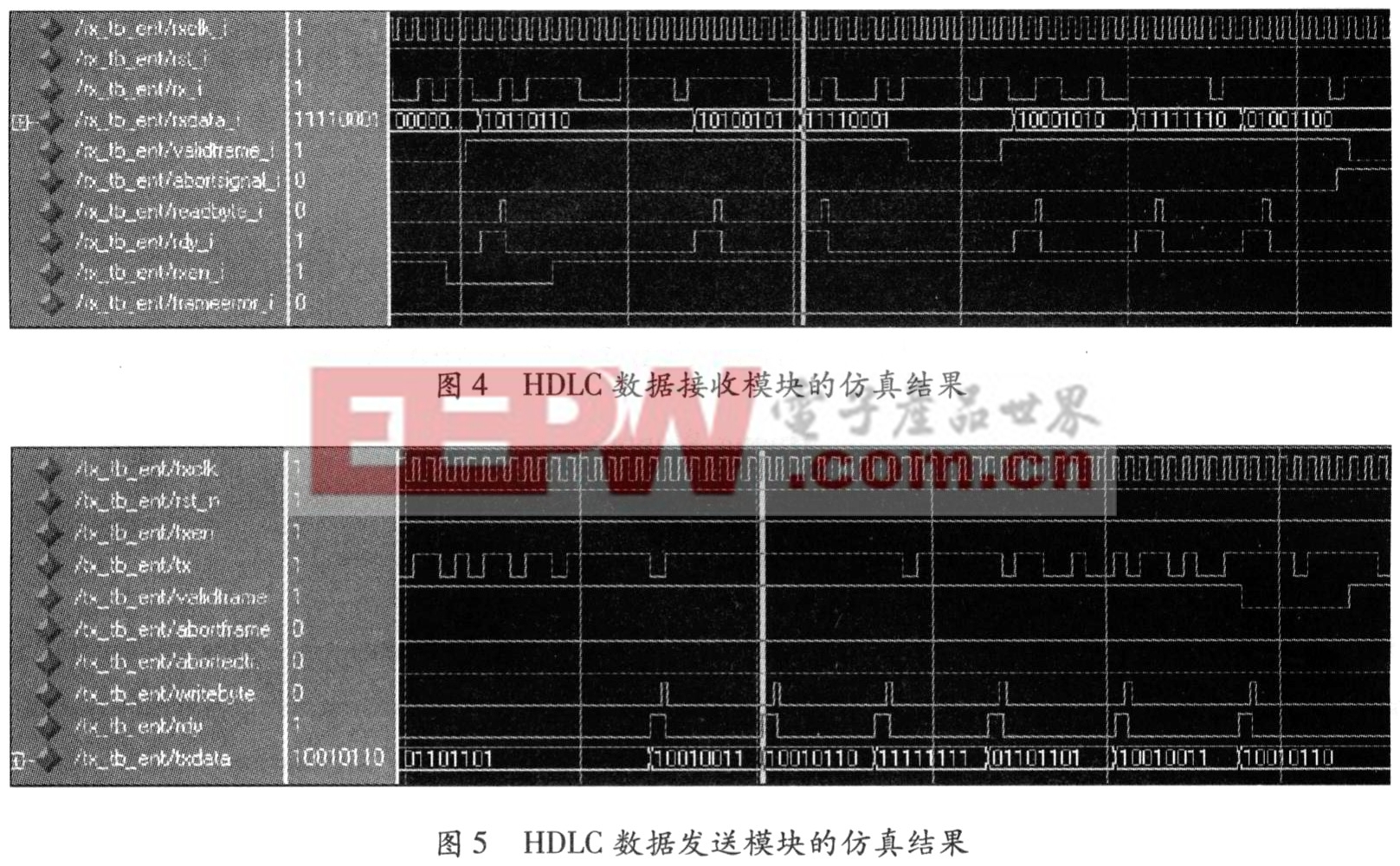

首先,在FPGA中實現一對HDLC數據收發電路,并在對收發電路進行仿真和相關測試。通過在Matlab開發環境下,生成相關的數據文件作為HDLC的數據源,在ModelSim SE 6.1的測試文件中直接調用,最后對比仿真結果和Matlab生成的數據源,可以得到滿意的結果。仿真的測試代碼覆蓋率為100%,仿真結果和數據源完全吻合,可以認定電路的正確性及良好的可靠性。圖4,圖5分別為HDLC數據收發模塊在ModelSim SE 6.1中的仿真圖。

為合理利用FPGA內部的邏輯資源,對設計進行一系列布局布線約束:(1)由前期的論證可知,設計的矛盾主要集中在資源的消耗上,所有模塊的優化目標定位為“Area”,除FIFO外,其他模塊規劃在一起;(2)將FIFO劃分為獨立的模塊;(3)全局時鐘綁定在Global資源上,并/串、串/并模塊中的衍生時鐘,根據和全局時鐘的關系,設定為多周期路徑。

實際數據收發的穩定性和可靠性,也跟單板、溫度等有關系。仿真完成后,在單板上進行飛線,對特定的收發電路進行電氣連接,進行回環測試法,即發送端輸出的數據由其接收端接收回來進行測試。在常溫下,經過30小時的長時間運行測試后,接收和發送的數據做了對比,沒有發現丟數據包和錯數據包的情況。由測試結果可知,該HDLC收發電路的具有穩定性和可靠性。高低溫實驗由于條件所限未進行,單板的溫度特性可由器件的溫度特性大概推知,這里不做討論。

4 結束語

針對某遙控遙測平臺的要求,文中提出了一種基于FPGA的多通道HDLC收發電路設計方案,并利用Altera公司的P2C70F672C8芯片來實現。目前,實現該電路的單板已經完成調試,并成功地應用于整機試驗。實踐表明,該電路實現簡單、可靠性高、使用靈活等優點,具有一定的推廣價值。

評論