基于FPGA的多通道HDLC收發電路設計

2 HDLC協議的FPGA實現

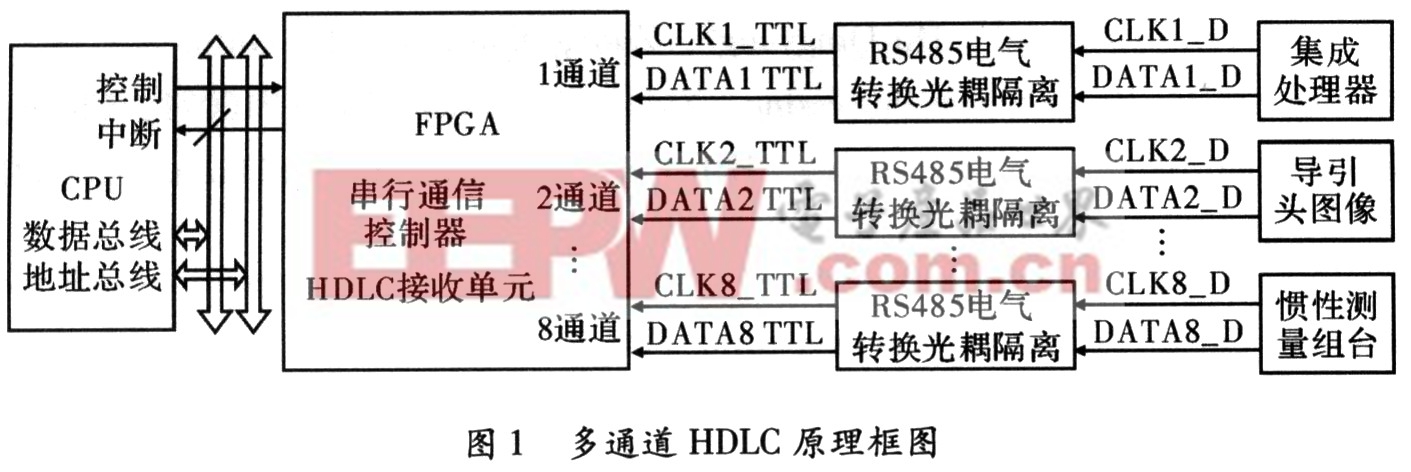

某遙控遙測平臺為確保滿足高速通訊、多通道收發、功能易于擴展配置的任務要求,中心控制器采用了以高性能的ARM7為CPU數據處理核心、采用FPGA設計串行通信控制器來收發多通道HDLC數據的一體化設計。本文引用地址:http://www.j9360.com/article/191874.htm

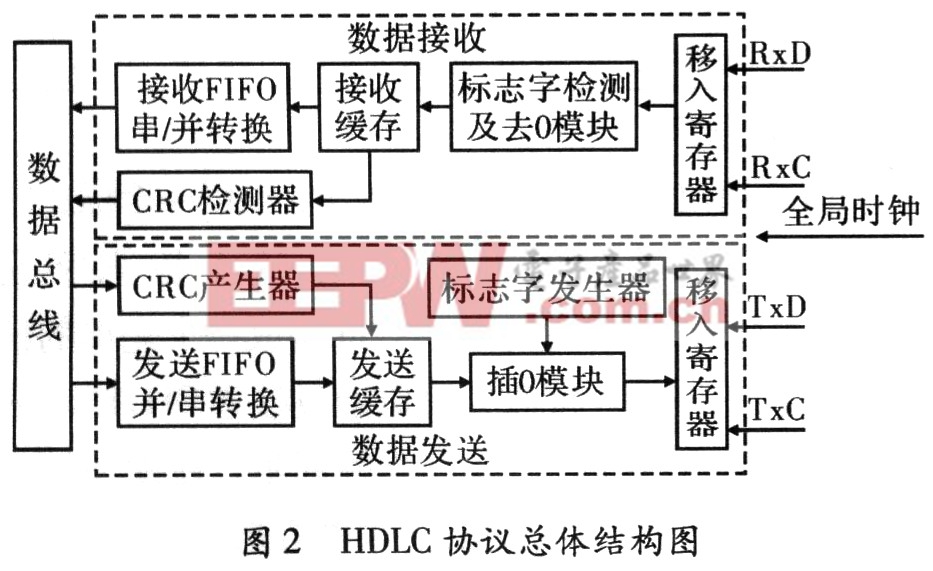

FPGA按照HDLC協議規程,接收并存儲來自集成處理器等8個獨立通道的數字量。系統先將外部輸入的HDLC數據流由RS485電氣特性轉換為TTL電平,在此過程中用光耦進行隔離,以避免與外部設備之間的相互干擾,并且RS485芯片與光耦器件的相關電源使用由電氣供給的獨立5 V和5 V地。 HDLC協議總體結構框圖,如圖2所示,每個控制模塊由時鐘控制、編碼/沖突檢測、發送和接收FIFO等功能模塊組成。在發送方向和接收方向,各有一個128 bit的FIFO,用于串行通道和CPU總線接口之間的數據緩沖。發送是接收的逆過程,這里以HDLC數據接收為例進行說明。

FPGA串行通信控制器接收HDLC數據的原理為:首先,將接收到的數據幀的消息字段和附加的狀態字段移入,然后根據選定的尋址模式,對接收幀中的目的地址進行識別,確認數據幀的發送地址是否為本設備(站地址=77H),是本設備數據幀則進行接收數據并存儲在FIFO中,當接收數據幀結束時,發出中斷信號給ARM系統,請求接收HDLC數據。

評論