基于FPGA技術的數字相關器的設計與實現

1 引 言

本文引用地址:http://www.j9360.com/article/191841.htm同步在通信系統中占有非常重要的地位,同步系統性能的高低在很大程度上決定了通信系統的質量,甚至通信的成敗。相關器是同步系統的關鍵部件之一,因此,要求相關器須有比其它部件更高的可靠性。實際應用中,相關器可用軟件實現也可用硬件電路實現,后者更適合于高速數據通信中的相關檢測。本文在總結一般數字相關器設計的基礎上,設計實現了一種高性能的數字相關器。

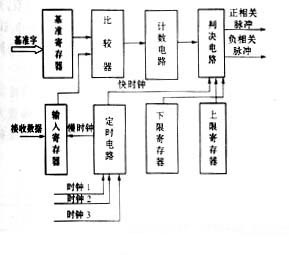

數字相關器的一般原理如圖1所示。

圖1 數字相關器的一般原理

相關器以數倍接收數據bit速率對所輸入的接收數據取樣,每個取樣bit移入數據輸入寄存器,然后逐bit地與存貯在基準寄存器中的基準字進行比較,若兩者一致,輸出正相關脈沖,若輸入數據bit與基準字補碼相一致,則輸出負相關脈沖。正相關和負相關所允許的最大不一致bit數分別存貯在相關器的上限寄存器和下限寄存器里。快時鐘頻率一般是慢時鐘的數十倍,相關計數判決在快時鐘的后半周之內必須完成。因此,時序控制比較復雜,而且輸出相關峰的寬度很窄(半個快時鐘周期),系統工作時容易造成丟峰、漏峰等不良后果,給系統帶來了潛在的不穩定因素,且增加了系統內在功耗。為此,本文提出一種用VHDL設計的在FPGA器件中實現的高速硬件相關器(無快時鐘,適時運算處理)的設計方法。

超級電容器相關文章:超級電容器原理

評論