采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創

人們對寬帶服務的帶寬要求越來越高,促使芯片供應商使用更多的高速串行收發器。因此,下一代應用采用了多種數據速率,從幾Mbps 到數百Gbps,在一種設備中集成了多種協議和服務。以太網等迅速發展的標準以及對提高數據速率的需求使得高速收發器成為主要的性能判定依據。標準單元ASIC 和ASSP 不具有人們需要的靈活性,其成本和風險無法讓用戶及時實現技術創新。本文介紹帶有收發器的全系列40-nmFPGA 和ASIC,發揮前沿技術優勢,在前一代創新基礎上,解決下一代系統難題。

引言

現代意義上的互聯網雖然只經歷了十幾年的時間,卻已經成為技術創新和帶寬增長的主要推動力量。更新現有通信系統以及新應用的出現要求采用更大的寬帶和更高的數據速率。今天,以視頻為主的網絡下載和點對點網絡連接( 文件共享) 占用了80% 的帶寬。流媒體( 視頻點播電影和電視)、IP 承載視頻和互聯網游戲等新應用占用的帶寬不到10% 。考慮到這些因素,互聯網仍處于發展初期,今后將持續強勁增長。

市場上最近推出的通信設備已經開始向40 甚至100 千兆以太網(GbE) 端口過渡,以更低的成本和功耗,在更緊湊的封裝中實現更大的帶寬。而且,摩爾定律還在不斷推動著半導體行業發展,集成電路上的晶體管數量每兩年就會加倍。新一代產品使用45-nm 或者40-nm 工藝來集成更多的功能,提高每一功能的工作性能和邏輯密度,降低功耗,而滿足日益增長的帶寬需求的關鍵則是更多、更快的高速串行收發器。

本文介紹高速串行收發器的發展趨勢,以及系統規劃人員和設計人員所面臨的挑戰。文章還回顧了某些特殊的市場需求,為滿足這些需求,可編程邏輯器件(PLD) 供應商必須提供帶有收發器的多種產品組合。這些器件具有豐富的邏輯、特性和I/O 功能,客戶利用它們能夠開發出滿足各種性能、功耗和成本目標的產品。

高速收發器技術的發展趨勢提高高速串行收發器的數據速率以及器件中收發器的數量可以實現更大的帶寬和更高的數據速率。使用以

下技術可以獲得帶寬達到100G 的接口:

■ 10 個10.3-Gbps 收發器(CAUI 協議)

■ 20 個6.375-Gbps 收發器(Interlaken 協議)

■ 40 個3.125-Gbps 收發器(XAUI 協議)

■ 100 個1.25-Gbps 收發器(SGMII 協議,注意,這只是用于演示目的,并不實用)

考慮到每個器件所有輸入和輸出數據通道的兩端口需求,如果收發器數據速率不能相應的提高,即使是采用最現代的工藝技術也難以滿足收發器的數量要求。

很多系統混合了DSP 模塊、控制處理器、ASSP、ASIC 和FPGA。系統規劃人員面臨的挑戰是對系統進行劃分,把這些器件連接起來,以滿足應用性能和帶寬要求。在很多情況下,由于ASSP 和ASIC 技術創新發展較慢,無法實現更快的接口。另一挑戰是這些器件所提供的各類協議,規劃人員不得不犧牲性能,重新使用原來的接口。這一般通過橋接器件――傳統的FPGA,連接原來的協議和新協議。解決這些問題最終會降低系統成本。

帶有收發器的數據鏈路不但支持更高的數據吞吐量,而且功效非常高,進一步提高了系統集成度,成為系統的關鍵組成部分。串化器/ 解串器(SERDES) 收發器是替代原有并行技術所必須采用的技術。通過使用收

發器技術,設計人員能夠解決當今高速數據鏈路設計中的關鍵問題:

■ 信號完整性:相對于并行接口,串行接口的延時和偏移都比較低。在串行協議應用,以及驅動背板方面,要求收發器具有優異的信號完整性,較低的抖動和誤碼率(BER)。

采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計Altera 公司

2

■ 復雜的電路板:使用串行接口可以減小電路板面積,減少所使用的電路板元件數量以及電路板層數。例如, PCI Express (PCIe) 接口將引腳和電路板面積減少了50%,而帶寬提高了一倍。

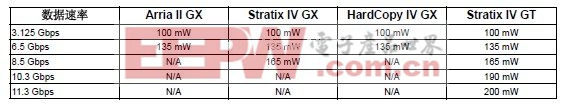

■ 功耗和散熱:串行接口的功耗要低于并行接口。例如,Stratix IV GT FPGA 的10G 接口在10.3 Gbps 時的功耗為190 mW, Altera 40-nm 收發器上的收發器 PMA 功率。表1 詳細列出了40-nm 工藝節點各種數據速率下的功耗。

總之,系統規劃人員面臨三種主要挑戰:

■ 在提高帶寬和數據速率時,需要更多、更快的收發器。

■ 既有原來的高速協議,又有各種不斷發展的新標準。

■ 符合背板和協議要求需要有優異的信號完整性。

收發器接口是系統規劃人員首先要考慮的關鍵因素,而器件選擇取決于所能夠提供的功能、性能、功耗和成本目標。最終,一定的市場需求決定了收發器系列產品最合適的功能。

市場需求

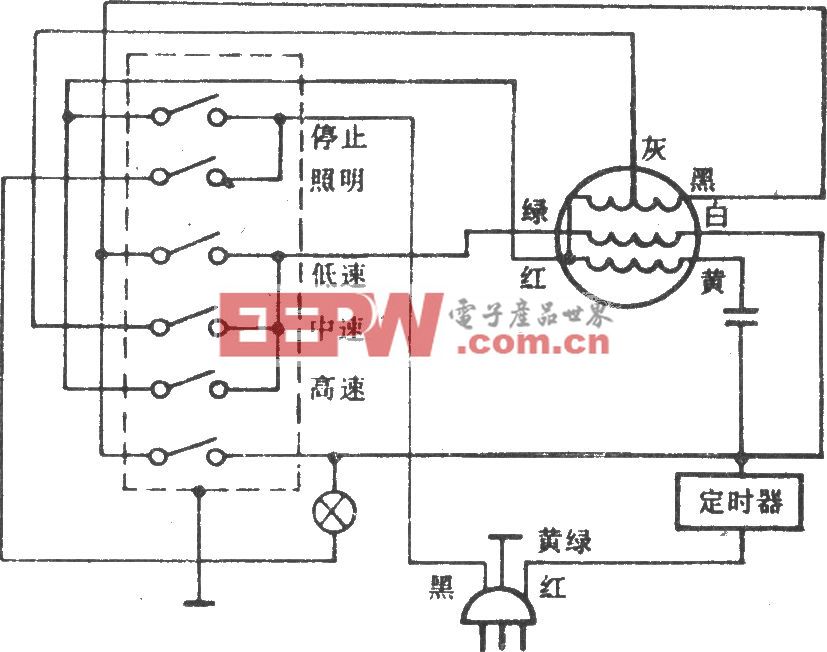

圖1 顯示了使用以太網協議的幾個例子,目前的通信基礎設施中使用了收發器。網絡中的每一部分都使用

了串行收發器技術,但是有不同的帶寬要求。越靠近用戶側,成本和功耗就越敏感,同時,帶寬也在降低,

收發器速率和數量也在減少。此外,隨著實際應用中處理需求的變化,器件密度和特性的關系也在不斷變

化。

圖1. 通信基礎設施中的收發器

表1. PMA 收發器功耗/ 通道對比

3

固網接入、傳輸和網絡設備

以太網已經發展成為當今應用最廣泛的物理層和鏈路層協議。而作為IEEE 標準802.3ae 于2002 年發布的10GbE 是目前最快的標準, IEEE正在制定40GbE和100GbE 以太網標準。網絡已經向數據包傳輸和全以太網設備過渡,應用范圍包括數據包處理和流量管理功能為主的橋接和全數據通道處理等(1)。根據網絡中靠近用戶的程度以及位置,帶寬從10 Gbps 至20 Gbps 發展到 40 Gbps 至80 Gbps,甚至是100 Gbps。并不存在能夠滿足所有需求的解決方案,因此,設備必須能夠支持不同的密度、特性、性能、功耗和成本目標。

關鍵需求推動了技術創新,包括對集成10G 收發器、高密度和高性能的需求,以及對以太網、GPON、CEI-6/Interlaken 和SONET/SDH 等協議標準的支持。

無線設備

過去,無線標準( 空中接口) 在發展過程中采用了不同的技術和物理通道,但是,對于3.9G/4G,更大的載波帶寬(20 MHz) 使得所有主要空中新接口使用OFDMA 技術。雖然正交頻分復用多址接入/ 多輸入多輸出(OFMDA-MIMO) 方法有可能在不久的將來實現技術融合,但目前的標準仍在不斷發展,繼續得以實施。

主要的無線需求包括在同一系統中對多種標準的支持,新一代體系結構中較強的信號處理能力,減少系統總延時等,所有這些需求都要求進一步提高集成度。而且,無線解決方案必須能夠靈活的延伸到名為毫微微基站( 以及微微基站、微基站和宏基站等) 的家庭基站中。這些市場和技術要求推動了高度集成方案的發展,最終成為芯片系統(SoC)。而且,這些收發器PLD 所具有的優點和其他解決方案具有可比性,甚至優于其他方案:

■ 在用戶數量或者每單元吞吐量上的成本和性能

■ 每Mbps 和每mm2 功耗和面積

■ 不同空中接口和協議的芯片間、卡對卡以及機箱之間接口高速收發器的靈活性和可更新能力

此外,很難有能夠滿足所有需求的通用解決方案。推動技術創新的關鍵需求包括更高的集成度,更低的成本,更好的性能,集成了DSP 功能的信號處理能力,以及支持CPRI/OBSAI 和Serial RapidIO® 等專用協議。

軍事、廣播、計算機和存儲、測試和醫療,以及其他市場領域

其他市場領域對收發器的需求各有不同,需要綜合考慮密度、性能、特性和功耗要求。PCIe Gen1 和Gen2以及以太網等標準協議得到了廣泛應用。某些市場對協議有特殊的要求,例如,廣播應用的SDI,以及計算機和存儲的SATA/SAS、HyperTransport 和QPI 等。由于很多應用只需要采用支持專用協議的收發器,因此, 10G 收發器在寬帶連接上迅速得到了應用,成為很多產品的主要技術推動力量。

關鍵技術

帶有收發器的FPGA 和ASIC 系列產品采用的技術包括工藝技術、支持可編程功耗技術的功耗和性能優化措施、邏輯架構、I/O、PLL、外部存儲器接口、高速串行收發器、時鐘數據恢復和時鐘產生、預加重和均衡,以及在PCIe 等協議上應用硬核知識產權(IP) 等。

評論