采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創

高速串行收發器

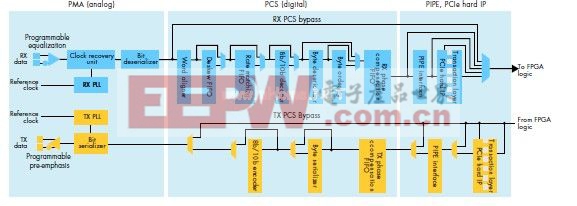

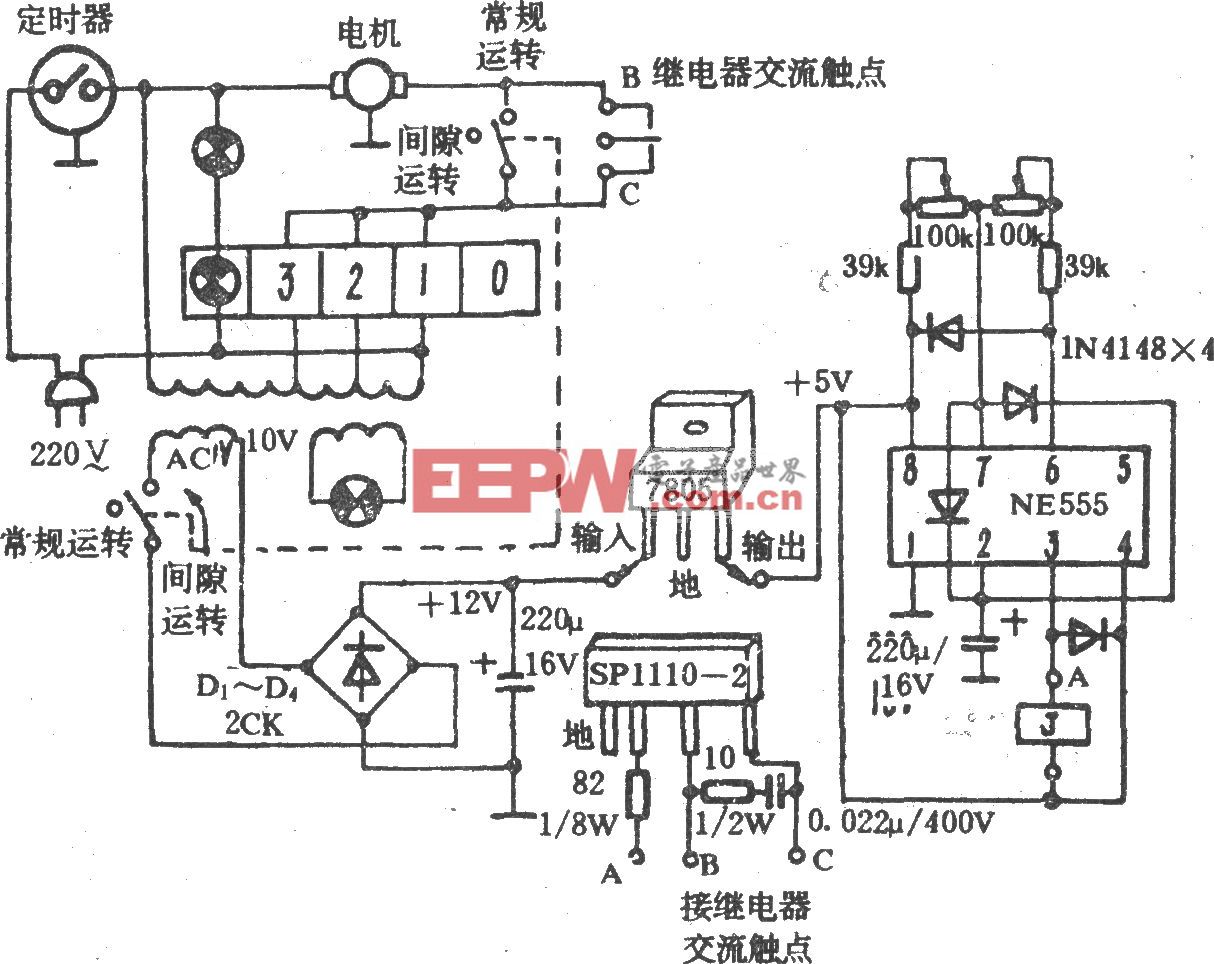

Altera的高速收發器模塊在物理介質附加(PMA)和物理編碼子層(PCS)使用通用體系結構(圖7所示)。 根據設計人員的不同要求,可以旁路PCS 中的模塊。

Altera 公司 采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計

7

圖7. PMA 和PCS 結構圖本文引用地址:http://www.j9360.com/article/191798.htm

PMA 功能可以用在模擬電路中,包括:

■ CDR

■ SERDES

■ 可編程預加重和均衡

■ I/O 緩沖,支持動態可控設置( 輸出差分電壓和差分OCT)。

PCS 提供數字功能以適應背板、芯片至芯片和芯片至模塊應用的多種關鍵協議。這些數字模塊為增強對協議的支持而進行了優化,減少了實現物理層協議所需要的器件資源,同時降低了功耗。與特定的IP 和參考設計相結合,這些模塊能夠提供完整的協議解決方案,縮短了設計周期,降低了風險。PCS 功能的例子包括8b/10b 編碼器/ 解碼器、相位補償FIFO 緩沖、字對齊器和速率匹配器,在收發器模塊中提供對協議的支持。

此外,還提供專用狀態機,支持PCIe、GbE 和XAUI 協議。

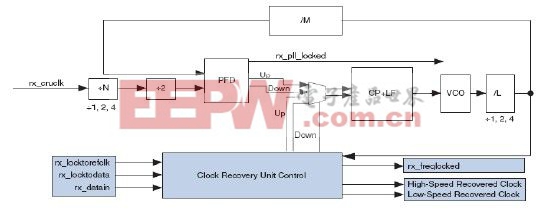

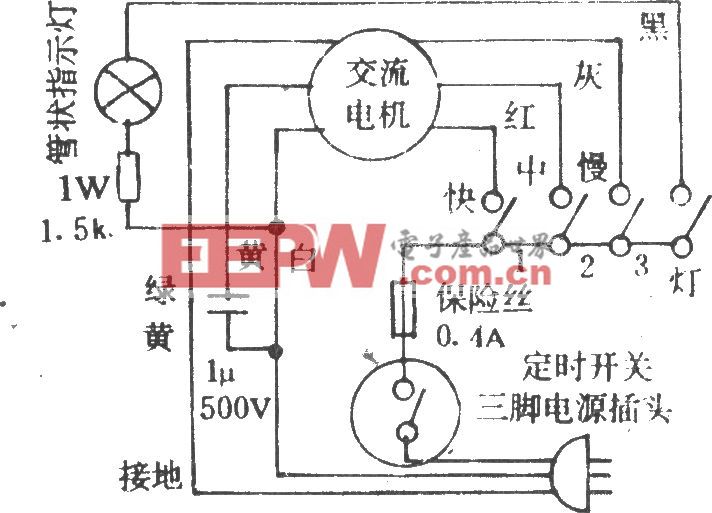

時鐘數據恢復

如圖8 所示, Altera 的高速CDR 電路使用混合體系結構,支持兩種工作模式,進一步發展了傳統的數據驅動體系結構。可以自動或者手動設置這兩種模式――鎖定至數據和鎖定至參考。采用參考時鐘作為輸入,將CDR 單元中的模擬PLL 鎖定到需要的頻率上。然后,電路從參考時鐘輸入切換到數據信號, CDR 和數據信號實現相位鎖定,從而恢復數據中的時鐘。這種體系結構的關鍵優勢在于縮短了鎖定時間,降低了功耗,能夠承受較大的抖動。結果, Altera 的收發器在驅動背板時,具有最低的抖動和最好的BER 性能,BER 達到10EC12 以上,而且協議兼容性非常好。

8

圖8. CDR 體系結構

時鐘產生和PLL 技術

時鐘產生是高速收發器的一項重要功能。時鐘抖動會影響發射器和接收器的性能,從而影響高速鏈路的BER 性能。PLL 的關鍵組成是振蕩器,它是抖動的主要來源。理想情況下,高速壓控振蕩器(VCO) 提供較寬的調諧范圍,較高的頻率(GHz),較低的噪聲和功耗,體積很小,集成度較高。

Altera 的高速收發器支持兩類振蕩器,環行振蕩器(RO) 和LC諧振振蕩器(LC諧振腔)。RO的集成度較高,功耗也比較低,管芯面積較小,在較寬的調諧范圍內都具有優異的抖動性能,每一接收通道都有獨立的RO,工作范圍在600 Mbps 至10.3 Gbps。然而,隨著頻率的提高,相位噪聲和抖動性能出現劣化,當高頻時需要優異的相位噪聲和抖動性能時, LC 諧振振蕩器則顯示出很大的優勢。LC 諧振振蕩器的缺點是其電感和可變電容( 變容),這些都是體積較大的元件。

■ 發送通道RO

● 在較寬的頻率范圍內具有優異的抖動性能

● 600 Mbps 至10.3 Gbps 的數據工作范圍

■ 發送通道LC 諧振振蕩器

● 技術實現了較好的抖動性能,較窄的工作范圍。

● 4.9C6.375 Gbps LC 諧振振蕩器,適用于PCIe/CEI-6。

● 9.9C11.3 Gbps LC 諧振振蕩器 ,適用于XLAUI/CAUI/CEI-11G。

預加重和均衡

所有傳輸介質普遍存在的一個問題是由頻率引起的損耗,特別是趨膚效應和電介質損耗導致的印刷電路板(PCB) 設計損耗。這種損耗導致高頻分量的衰減更大,從而降低了遠端信號的接收能力,縮短了驅動長度,增大了BER。預加重和均衡用在Altera 的高速收發器中,以克服傳輸損耗,驅動帶有兩個連接器的40

FR-4 背板。

在數據信號發送至通道之前,高速收發器的發射器采用預加重技術放大數據信號的高頻分量。由于所生成數據信號的前面和后續數據位在發射器中是確定的,因此,預加重方法應用在相對于主脈沖的不同數據位上。Altera 的預加重方案使用預抽頭,其后是主脈沖和兩個后抽頭。

在接收器開始進行均衡,當數據進入接收器時,均衡起到了高通濾波器的功能,成功地重建信號。Altera的高速收發器支持各種均衡方案(4):

Altera 公司 采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計

9

■ 連續時間線性均衡(CTLE)

■ 自適應散射補償引擎(ADCE)(5)

■ 判定反饋均衡(DFE)

由于不同的數據速率和背板特性,因此,很難從數千種設置中選擇最佳均衡設置。使用收發器HSPICE 模型和背板S 參數特性進行仿真可以簡化這一過程。但是,某些應用在工作中需要插拔系統卡,當條件變化時,不得不迅速更新均衡設置。利用即插即用信號完整性功能, Altera 引入了ADCE,熱插拔收發器支持在40 FR-4 背板上2.5 Gbps 至6.5 Gbps 的數據傳輸。

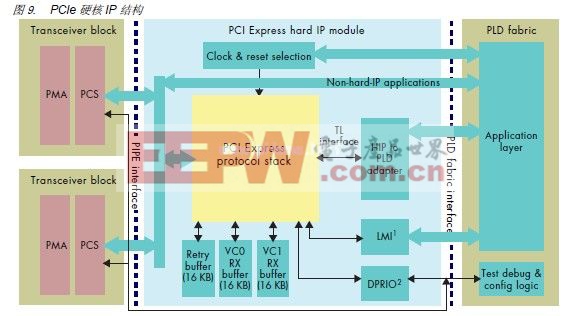

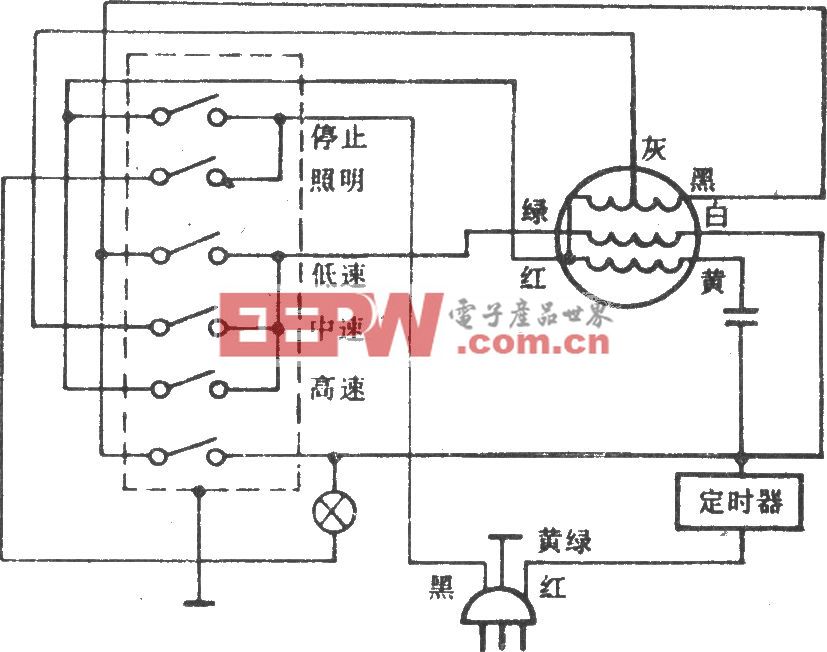

面向PCI Express 的硬核IP

PCIe 的廣泛應用推動了集成PCIe 功能的發展,在實際中它作為預驗證和符合標準的硬核IP 模塊來實現。

PCIe 的重要優勢是能夠大大節省資源( 最大40K LE),降低功耗,其編譯時間更短,從而縮短了設計周期。

如圖9 所示,硬核IP 模塊嵌入在PCIe 協議棧的所有層中,包括收發器模塊、物理層、數據鏈路層和協議層。PCIe 硬核IP 模塊符合以下PCI-SIG 規范:

■ PCIe 基本規范, Rev 1.1 (2.5 Gbps)

■ PCIe 基本規范, Rev 2.0 (2.5 和5.0 Gbps)

圖9. PCIe 硬核IP 結構

注釋:

(1) LMI:本地管理接口

(2) DPRIO:動態部分可重新配置輸入/ 輸出

Altera 的收發器系列器件

新器件的發展符合摩爾定律――密度每兩年加倍,開發新器件需要不同的方法,由于開發成本隨之增加,應盡量采用相關的技術。在開發全系列收發器FPGA 和ASIC 時, Altera 采用了以下方法:

■ 重新使用已有工藝所采用的技術

■ 通過技術進步,發揮每一新工藝節點的優勢來逐步改進。

10

■ 使用通用體系結構,綜合考慮不同的性能、功耗和成本要求,優化構建模塊。

■ 進行革命性的創新,以滿足重新使用已有技術所不能解決的需求。

系列產品組成

基于TSMC 的40-nm 工藝, Altera 采用了相同的成熟收發器體系結構來開發每一帶有收發器的FPGA 和ASIC,這種結構非常適合寬帶串行接口應用。在每個器件中,集成收發器模塊針對目標應用進行了優化。

Arria II GX FPGA

Arria® II GX FPGA 滿足了對成本和功耗敏感的應用,在低密度和中密度范圍內提供豐富的特性。最大收發器數據速率是3.75 Gbps,滿足了GPON、IP DSLAM、遠程射頻前端、廣播和橋接等中等性能應用領域對高速協議和寬帶的需求。收發器和I/O 經過優化,綜合考慮特性和性能,具有較高的性價比。雖然Arria IIGX FPGA 的固定功耗模式不具有可編程功耗技術的靈活性,但是,它大大降低了靜態功耗。Arria II GXFPGA 采用可編程預加重和均衡技術,適合背板應用,并且具有優異的信號完整性。由于只有速率較高的背板應用才需要ADCE 和DFE 等功能,為降低成本和功耗,該器件不支持這類功能。

Stratix IV GX FPGA

Stratix IV GX FPGA 提供最大的密度,最好的性能以及最低的功耗,收發器速率高達8.5 Gbps, 48 個收發器提高了帶寬,其豐富的功能可支持背板應用和高速協議。關鍵應用包括對性能要求較高的無線基站、40G/100G 應用、高端路由器和橋接應用。其優異的信號完整性保證了與PCIe Gen2 和CEI-6 等嚴格協議的兼容性。可編程功耗技術提高了設計中關鍵時序通路的性能,同時優化了性能較低部分的功耗。

評論