基于CPLD的數據采集與顯示接口電路仿真設計

摘要:常規數據采集與顯示方法是應用CPU或DSP通過軟件控制數據采集的模/數轉換,這樣將會頻繁中斷系統的運行,從而降低系統的運算速度,數據采集的速度也將受到限制。通過CPLD實現由硬件控制模/數轉換和數據顯示,最大限度地提高系統的信號采集和處理能力。這里運用VHDL硬件編程語言,通過狀態機設計程序,完成A/D轉換芯片與可編程邏輯芯片的接口。將A/D轉換結果以BCD碼形式通過CPLD芯片進行顯示,實時觀測轉換進程,給出了BCD碼轉換流程圖,完成相應電路設計,通過QuartusII軟件進行仿真,并在開發系統上成功實現功能驗證,提高了系統的運算速度。

關鍵詞:可編程邏輯器件;模數轉換;二-十進制碼顯示;接口電路

0 引 言

CPLD稱為復雜可編程邏輯設計芯片,它是大規模可編程器件,具有高集成度、高可靠性、高速度的特點。CPLD是利用EDA技術進行電子系統設計的載體。硬件描述語言是EDA技術進行電子系統設計的主要表達手段,VHDL語言是常用的硬件描述語言之一;軟件開發工具是利用EDA技術進行電子系統設計的智能化的自動化設計工具,常用開發工具有QuartusII,Ispexpert,Foundation等。CPLD以高速、高可靠性、串并行工作方式等特點在電子設計中廣泛應用。它打破了軟硬件之間的界限,加速了產品的開發過程。同樣單片機具有性價比高、功能靈活、良好的數據處理能力等特點。CPLD芯片與單片機結合在高性能儀器儀表中應用廣泛。

1 電路的仿真設計

1.1 硬件電路功能

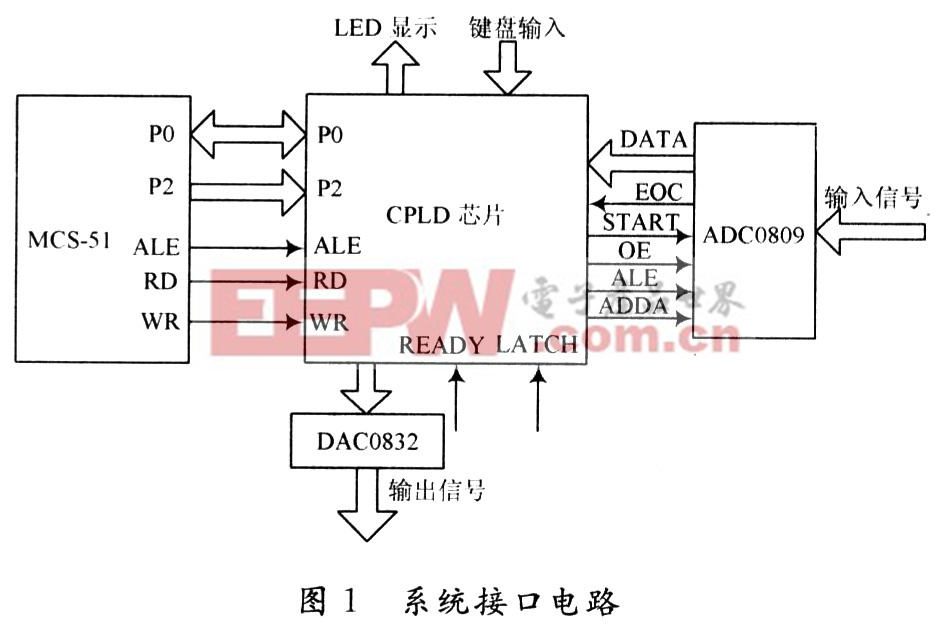

用一片MCS-51芯片、一片CPLD/FPGA芯片、模/數轉換器ADC0809和數/模轉換器DAC0832構成一個數據采集系統,并用CPLD/FPGA實現數據采樣、D/A轉換輸出、有關數據顯示的控制,單片機完成對A/D轉換數據運算。電路如圖1所示。

系統功能如下:系統按一定速率采集輸入電壓Ui,經AD0809轉換為8位數字量data;輸入數據與通過CPLD/FPGA采樣后輸入單片機進行相關運算,最后通過CPLD/FPGA送至DAC0832轉換為△U;數據采集和處理均在數據采集系統控制器的管理下有序進行。工作速率由時鐘信號CLK的速率決定。

1.2 單片機與CPLD/FPGA接口設計

單片機采用以總線方式與可編程芯片進行數據與控制信息通信,此方式有許多優點:

(1)速度快。其通信工作時序是純硬件行為,對于MCS-51單片機只需一條單字節指令就能完成所需的讀/寫時序如MOV@DPTR A和MOVA@DPTR。

(2)節省CPLD芯片的I/O口線。如果將圖中的譯碼器設置足夠的譯碼輸出以及安排足夠的鎖存器就能僅通過19根I/O口線在FPGA/CPLD與單片機之間進行各種類型的數據與控制信息交換。

(3)相對于非總線方式單片機的編程簡捷控制可靠。

(4)在FPGA/CPLD中通過邏輯切換單片機易于與SRAM或ROM接口。這種方式首先由FPGA/CPLD與接口的高速A/D等器件進行高速數據采樣并將數據暫存于SRAM中。采樣結束后通過切換使單片機與SRAM以總線方式進行數據通信以便發揮單片機強大的數據處理能力。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論