基于FPGA的Kalman濾波器的設計

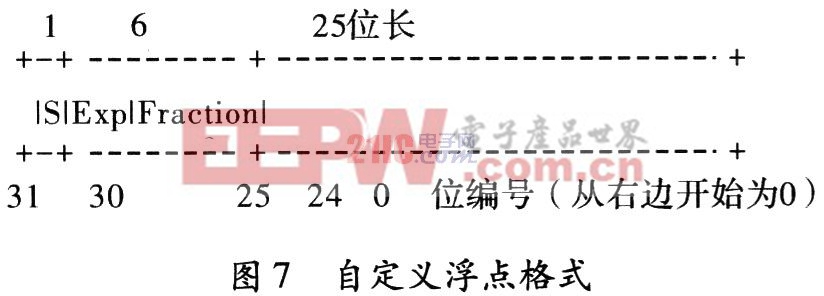

由于資源的限制,濾波中的運算過程只能以有限的精度進行,但過低的精度容易引起濾波發散,同時為了兼顧A/D高達24 bit的分辨率精度,在IEEE754單精度浮點數格式的基礎上按照浮點表示的原則做了改造,將指數部分減少到6位,尾數增加到25位,25位尾數可以完全表示A/D輸出的24位采樣值,并削弱舍入誤差的影響,其格式如圖7所示。本文引用地址:http://www.j9360.com/article/191740.htm

本系統對處理速度的要求并不高,運算部件的設計并不考慮速度優化。

加法器按以下通用的規則設計:

(1)階碼相減:兩個操作數階碼相減,求得階差d=|Ea-Eb|;

(2)尾數對齊:階碼小的操作數的尾數右移d位;

(3)尾數相加:完成移位處理后的尾數相加運算;

(4)轉換:尾數相加的結果為負數時,轉換為符號尾數的表示方式;

(5)前導0/1的判定:判定由于減法結果產生的左移位數,對于加法判定是否右移一位或不移,對前導0/1判定的結果進行編碼以驅動規格化移位;

(6)規格化:規格化有效位并且根據移位的方向和位數修改最終的階碼Ef;

(7)舍入:根據IEEE標準判定最終結果的舍入,如果需要入,則最末有效位加1;如舍入引起溢出,則需要有效位右移1位,同時階碼Ef加1。

乘法器的設計相對簡單,與加法器一樣采用簡單的設計規則:

(1)指數相加:完成兩個操作數的指數相加運算;

(2)尾數調整:將尾數f調整為l/f的補碼格式;

(3)尾數相乘:完成兩個操作數的尾數相乘運算;

(4)規格化:根據尾數運算結果調整指數位,對尾數進行舍入截位操作,規格化輸出結果。

采用Altera提供的IP核,除法器能完成IEEE754單精度除法運算。數據進入該除法器前需要將自定義的浮點格式的階碼擴展為8位加上95,尾數右移兩位,轉換為標準單精度浮點,計算結果再由標準單精度浮點的按相反的方法轉換為自定義浮點。

文中硬件編程語言是用Verilog實現的。

4 實測結果分析與結論

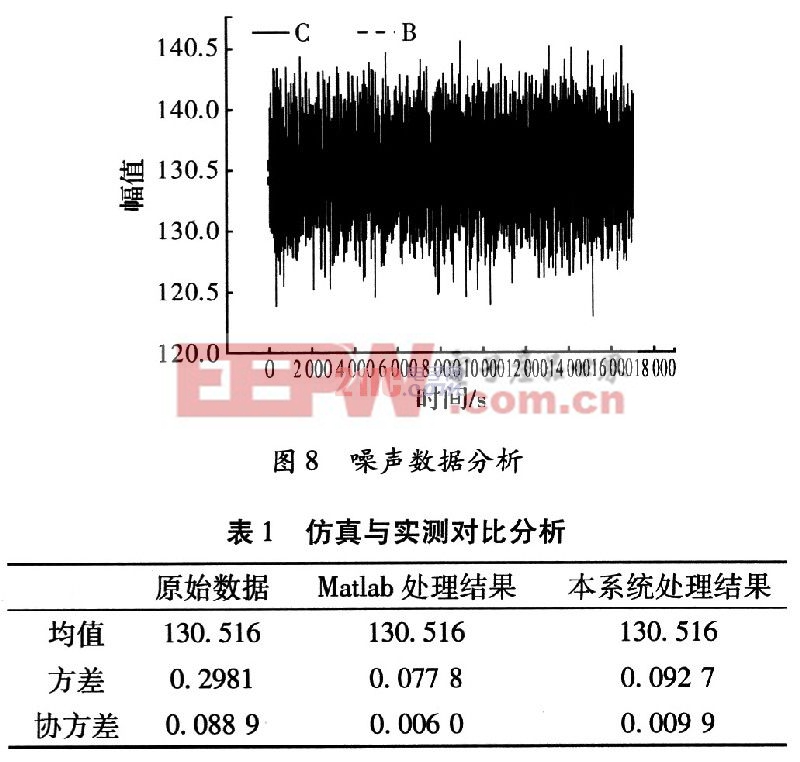

從系統輸出數據中隨機抽取一段數據用Matlab分析,其結果如圖8所示。實線C表示的是濾波前的噪聲:虛線B表示的是濾波后的噪聲。很容易看出經過濾波后噪聲降低了很多。仿真與實測對比分析如表1所示。

5 結束語

卡爾曼濾波器在很多領域具有重要的作用,可以實現數字信號處理功能,并能滿足實時性的要求。用FPGA實現Kalman濾波過程,實現簡便、成本較低、濾波效果好,被廣泛應用于圖像視頻、陀螺慣導去噪、電子羅盤、雷達接收機目標跟蹤處理、目標預測等圖像、數據采集與處理領域。

評論