基于DSP和FPGA的實時圖像壓縮系統設計

1 系統工作原理及硬件設計

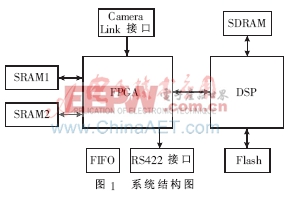

系統由Camera Link接口模塊、以FPGA為核心的圖像采集預處理與傳輸單元、以DSP為核心的圖像壓縮單元以及RS422遠距離數據傳輸單元組成。由于采集、處理均需要訪問存儲器,為了降低成本,采用普通的異步SRAM,按功能區分可分為采集SRAM和壓縮處理SRAM。讀寫邏輯由FPGA控制,采用乒乓機制進行切換。整個系統結構如圖1所示。

系統工作過程:圖像信號經由LVDS轉換芯片后轉換成LVTTL信號,直接傳送至FPGA解碼為8位數據,以字節方式一行一行寫入SRAM靜態存儲器(存儲器由兩部分組成),用于乒乓緩存輸入數據,每部分滿1幀后由FPGA控制送出幀中斷給DSP,DSP啟動EDMA讀入1幀數據,采用JPEG2000方式編碼后連續寫入到FIFO_OUT,FPGA負責從FIFO_OUT讀出數據,非空即讀,緩存積累不會超過1幀數據。讀出的數據另行打包后以9 Mb/s的碼率通過DS26LV31 422接口芯片從out1接口輸出,或者分流后從out1和out2以各4.5 Mb/s的碼率輸出。

2 FPGA功能模塊設計

2.1 Camera Link接口模塊

Camera Link接口模塊負責對高頻幀數字攝像頭輸出的LVDS信號轉換為TTL標準信號。

關于Camera Link的采集數據的邏輯代碼,關鍵之處在于產生存儲器的地址信號、存儲器寫信號以及在對應的地址處將數據穩定地寫進存儲器。本系統用像素時鐘產生列地址計數器、行同步信號產生行地址計數器,兩者拼接產生存儲器的地址信號。這樣產生的有效地址雖然不連續,但意義明確,而且有利于顯示部分的隔行隔列顯示。對于8 bit的數據,可將2個有效數據拼接成16 bit后再存儲,這樣可以提高FPGA讀寫存儲器的速度。

Camera Link接口時序如圖2所示。

圖2中:VD為幀同步信號,電平模式,高電平有效;HD為行同步信號,脈沖模式,上升沿有效;PCLK為像素同步時鐘,脈沖模式;DATA為10 bit圖像數據,在PCLK的下降沿推出,接收端在PCLK上升沿采集,PCLK為常運行模式。每個VD有效期內有480個HD有效信號,在第0~478個HD有效時,每個HD有效期間有600個有效圖像數據,第479個HD(即每幀的最后1行)有效時,前600個DATA為有效圖像數據,600個DATA后預留6個字節輸出圖像相關信息,即第D600~D605為預留字節。

2.2 SRAM乒乓緩存

在圖像采集處理系統中,DSP的壓縮算法在實現時間上往往并不是固定不變的,然而前端的采集模塊卻使用均勻速度對圖像進行采集,這樣存在時間上的不同步,有可能會導致圖像數據的丟失和影響幀數據的完整性[2]。為此,本系統在采集和壓縮模塊之間增加1個緩沖電路來解決這一問題。

常用的緩沖電路主要有3種[3]:雙口RAM結構、FIFO結構和乒乓結構。由于乒乓結構可以使用相對比較便宜的高速大容量SRAM,而且可以實現數據的連續性,因此本系統采用了乒乓結構雙SRAM作為視頻數據的緩沖。在將1幀圖像的數據全部存儲完以后,DSP再利用很短的時間直接將1幀圖像數據讀入片內,這樣既可以保證不丟失像素數據、DSP可以連續采集每1幀像素數據,又能為DSP留出更多空余時間,為后面進行圖像處理提供可能。為了實現數據幀的完整性,必須保證讀取數據幀的優先級要高于寫數據幀的優先級,所以本系統的數據輸入輸出單元是根據數據處理流程來進行切換的。

評論