利用ADMS平臺加速混合信號集成電路設計

3. Mach

SPICE仿真的特點是精度高、速度慢。做模擬電路設計時,用SPICE仿真一般可以滿足要求。但是當電路規模增加、尤其是增加了晶體管級描述的數字電路部分之后,SPICE顯得過慢。相同的仿真條件下,SPICE的仿真時間隨著晶體管的增加甚至不是線性上升,而是呈指數次方上升。這樣電路仿真成為設計的瓶頸,這一點在后仿真階段也經常遇到。

于是Mach作為Fast-SPICE應運而生。Mach在Eldo的基礎上,通過查表方式的晶體管模型迅速提高了仿真速度。相比Eldo,Mach可以將仿真速度提升10~1,000倍。速度提升犧牲的是精度,不過損失的精度能夠控制在3%之內。Mach的處理容量也是非常巨大的,最大可以達到2,000萬個器件。于是對于一些精度要求不是非常嚴格的設計,當需要快速驗證時,Mach成為必需,如存儲器設計。

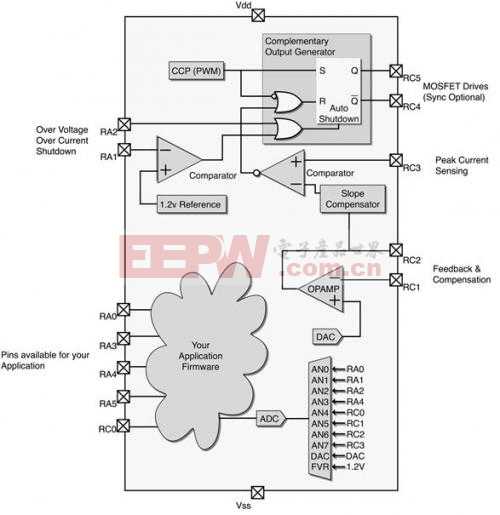

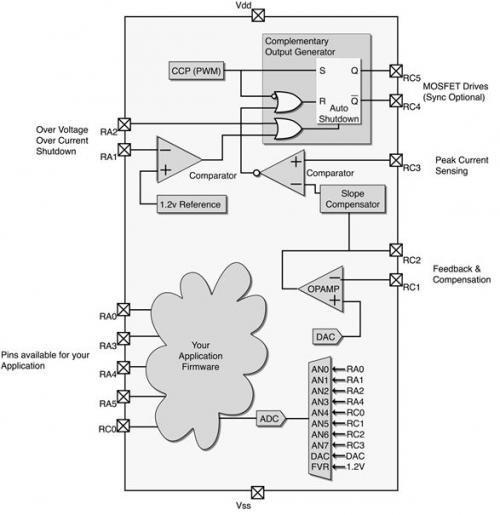

ADMS是一個混合信號驗證平臺,集成了以上三種工具的技術。對模擬電路部分,采用Eldo的仿真算法,或者Mach的快速仿真算法;對數字部分,采用ModelSim的仿真算法。但是ADMS并不是這些工具簡單拼起來,它有單一的內核引擎。

采用ADMS進行設計,傳統的數字設計流程和模擬設計流程被打散并重新組合,設計師可以在任何階段對電路進行驗證,數字設計和模擬設計通過ADMS組成一個整體。

最新發布的ADMS4.0版增加了SystemVerilog語言和SystemC支持,這使得ADMS支持的語言達到了八種,即VHDL、Verilog、SPICE、VHDL-AMS、Verilog-AMS、SystemVerilog、SystemC 以及C,涵蓋了目前大部分的集成電路設計語言。這使得用ADMS進行設計時方法靈活多變,而工具卻只有一個。輸入ADMS的文件可以只有一個,不管其中的內容是HDL、SPICE,還是C語言,ADMS都可以讀入,并自動進行處理,給出仿真結果,例如在模擬電路中引入一個HDL描述的IP,或者是工具附帶單元庫里的一個VHDL-AMS行為級描述的運放單元,各種語言可以無縫地組合到一起。

ADMS提供了靈活的使用方式。它既可以集成到Mentor Graphics的電路圖編輯工具DA-IC中,也可以集成到Cadence的Schematics Composer中(圖3),另外還可以單獨使用。應用時ADMS的界面與經典的ModelSim相似,操作簡單,其樹狀結構顯示使得整個設計一目了然。使用時只需要讀入輸入的各種文本文件(可以以數字結構為最頂端層次,也可以以模擬結構為最頂端層次),即可由ADMS進行仿真和調試。

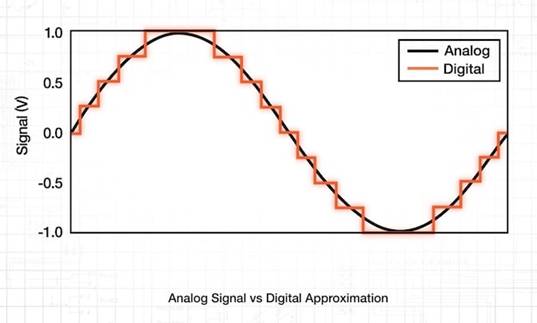

ADMS的輸出文件可以被其它工具的多種波形觀察工具查看和計算,不過ADMS附帶有兩個功能強大的波形處理工具Xelga和EZwave,可以同時處理數字和模擬信號,并進行各種操作與運算。

Eldo RF在Eldo的基礎上發展而來,針對射頻電路使用了新的技術,ADMS也可以擴展到ADMS RF,成為針對射頻混合信號SoC設計的工具。

ADMS附帶了很多行為級描述的單元庫,稱為CommLib,其中包括三百多種常見的基本單元,如ADC、DAC、PLL、Σ-Δ、OP等等。各種庫提供了大量的接口參數供修改,在設計中可以直接調用這些單元庫,增加仿真速度,以及方便調試電路。CommLib還有一個“行為級模型校正”(BMC,Behavior Model Calibration)的功能,通過BMC以及ADMS的驗證,可以將所設計的電路圖抽象到行為級。在仿真的時候,行為級的仿真速度比晶體管級快1,000倍,這樣可以將部分電路抽象到行為級,從而增加仿真速度,并方便調試。抽象化技術在大規模電路設計中越來越得到頻繁應用。

本文小結

ADMS是一種真正意義上的模擬/混合仿真工具,它可提供全面的語言與設計方法支持。目前,中國真正在做混合信號設計的設計師雖然不多,但毫無疑問,正在逐漸增加。那么,究竟在什么樣的情況下,需要轉到混合信號設計呢?也許可以簡單地作這樣一個描述:當使用HDL仿真器的數字電路設計工程師面臨增長的模擬部分和模擬電路行為,卻苦于不足的模型以及仿真精度時;當使用SPICE或者FastSPICE的模擬電路設計工程師,面臨增長的數字復雜度以及大規模,苦于仿真速度過慢時。這些時候,采用混合信號設計,就可以提升設計速度和效率以及設計水平,并降低產品成本。

評論