Cadence與聯電合作開發28納米HPC+工藝中模擬/混合信號流程的認證

聯華電子今(6日)宣布Cadence?模擬/混合信號(AMS)芯片設計流程已獲得聯華電子28納米HPC+工藝的認證。 透過此認證,Cadence和聯電的共同客戶可以于28納米HPC+工藝上利用全新的AMS解決方案,去設計汽車、工業物聯網(IoT)和人工智能(AI)芯片。 此完整的AMS流程是基于聯電晶圓設計套件(FDK)所設計的,其中包括具有高度自動化電路設計、布局、簽核及驗證流程的一個實際示范電路,讓客戶可在28納米的HPC+工藝上實現更無縫的芯片設計。

本文引用地址:http://www.j9360.com/article/201908/403461.htmCadence AMS流程結合了經客制化確認的類比/數位驗證平臺,并支持更廣泛的Cadence智能系統設計?策略,加速SoC設計的卓越性。 AMS流程具有整合標準組件數字化的功能,非常適合數位輔助類比的設計,是客戶使用28納米HPC+工藝,開發汽車、工業物聯網和AI應用的理想解決方案。

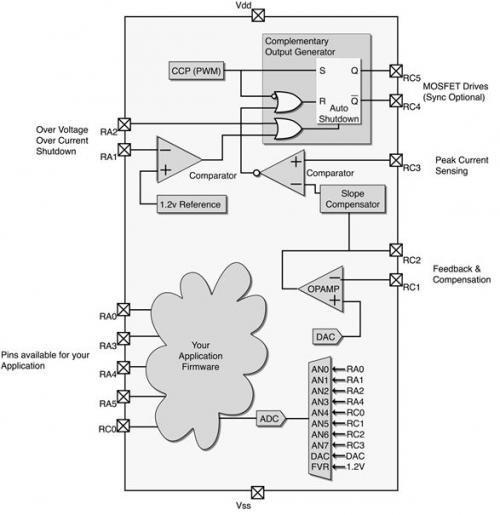

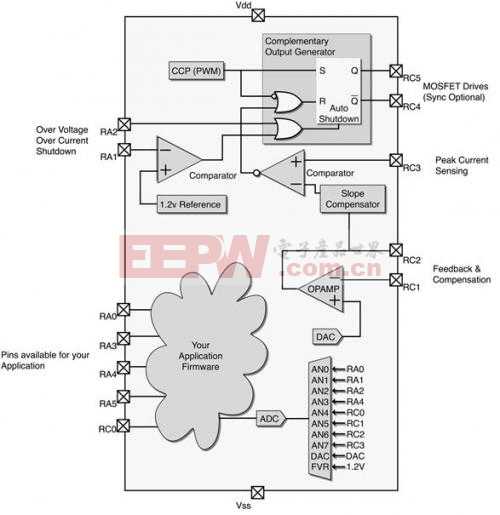

經過認證的完整AMS流程包括Virtuoso?仿真設計環境(ADE),Virtuoso圖形編輯器,Virtuoso布局套件,Virtuoso空間基礎繞線器,Spectre?平行加速仿真器(APS),帶有整合Xcelium?平行邏輯仿真引擎的Spectre AMS Designer,Voltus?-Fi客制化電源完整性解決方案,Innovus?實施系統,Quantus?寄生效應萃取解決方案和物理驗證系統(PVS)。 該流程提供以下內容:

l前端設計:提供控角、統計和可靠性模擬; 電路和組件檢查,以及類比和混合信號仿真和驗證管理。

l客制布局設計:提供先進的電遷移和寄生感知環境,包括圖形驅動布局和模塊生成、線編輯器和引腳到主干的布線、符號置放、電子感知設計和壓敏規則。

l后布局的寄生模擬和電遷移及電位降(EM-IR)分析與整合簽核:包括寄生組件參數擷取,電路布局規則檢查(DRC)和電路布局驗證(LVS)檢查。

l混合信號OpenAccess:在單個OpenAccess設計數據庫上運行的Virtuoso和Innovus平臺之間實現完全互動能力,使混合信號設計人員能夠直接在Virtuoso環境內使用Innovus工具,且能無縫地執行數字區塊的實作。

Cadence的客制化IC與PCB部門產品管理副總Wilbur Luo表示:「Cadence與聯華電子合作,提供了經28HPC+技術認證的AMS整合設計流程,該技術基于Cadence業界領先的客制模擬/數字和簽核以及驗證平臺。此認證推動了SoC設計的卓越性,使得聯電的客戶得以利用先進的功能工具組,進行電路設計、性能與可靠性驗證、自動布局以及區塊和芯片整合,使他們能夠在汽車、工業物聯網和AI應用芯片設計上更有十足的把握。」

聯華電子量產就緒的28納米HPC+工藝采用高介電系數/金屬閘極堆棧技術,廣泛支持各種組件選項,以提升彈性及符合效能需求,同時針對多樣的產品系列,例如應用產品處理器、手機基頻、Wi-Fi,數字電視 / 機頂盒,毫米波等具備高介電系數/金屬閘極堆棧及豐富的組件電壓選項、內存字節及降頻/超頻功能,有助于系統單芯片設計公司推出效能及電池壽命屢創新高的產品。

聯華電子硅智財研發暨設計支持處林子惠處長同時表示:「透過與Cadence的合作,結合Cadence AMS流程和聯電設計套件,開發了一個全面而獨特的設計流程,為我們在28納米HPC+工藝技術的芯片設計客戶提供可靠與高效的流程。憑借此流程的功能優勢,提供用戶詳細說明,以利客戶透過聯華電子的流程提升生產力,可更快地將下一代的創新產品推向市場。」

評論