基于FPGA的數字示波器

摘要:提出一種基于FPGA的簡易數字示波器設計方法,硬件上采用以Altera公司的EP2C8Q208CN現場可編程門陣列芯片作為核心器件,同時結合FPGA和NIOS軟核的優勢,設計高效的片上可編程系統(SoPC)對高速A/D所采集的數據進行快速存儲和處理。整機測試表明,系統各功能正常,整個系統集成度高,體積小,可靠性高,易于程控,使用靈活。

關鍵詞:現場可編程邏輯門陣列;信號調整;高速A/D;片上可編程系統

高速數字化采樣技術和FPGA技術的發展對傳統測試儀器的體系結構,包括傳統測量方法、傳統儀器的定義和分類等都產生深刻的影響。伴隨數字技術的發展,數字示波器展現了其強大的功能:智能捕獲、參數分析、時頻等變換處理、超大規模數據波形存儲以及數據上網共享等。與傳統模擬示波器相比,數字示波器不僅具有可存儲波形,體積小,功耗低,使用方便等優點,而且還具有強大的信號實時處理分析功能。

1 系統組成

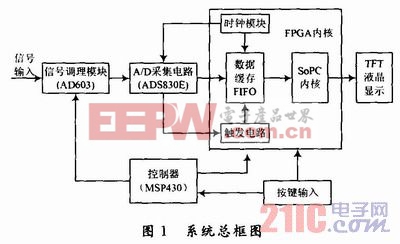

設計的數字示波器總體框圖如圖1所示。

系統主要包括信號調理模塊、A/D轉換模塊、控制器模塊、時鐘產生模塊、觸發電路、數據緩存模塊、數據快速處理模塊、輸入模塊及顯示模塊。控制器模塊由MSP430單片機組成,用來控制信號調理模塊和A/D轉換模塊以及按鍵輸入;時鐘產生模塊、數據緩存模塊,數據快速處理模塊這三個部分在FPGA內部完成;數據快速處理模塊是由基于FPGA的SoPC來完成的,同時SoPC還控制TFT液晶的顯示。

2 系統理論分析及硬件實現

2.1 信號調理模塊

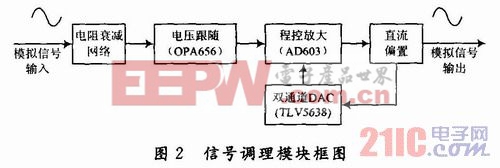

信號調理電路包括衰減網絡、電壓跟隨電路、程控放大電路和直流偏置電路等。信號調理電路框圖如圖2所示。

為了保證輸入信號在AD芯片的參考電壓范圍內,當大信號輸入時,必須通過衰減網絡對其進行衰減,以滿足A/D采集電路的電壓要求。通過電阻網絡分壓實現信號的衰減,衰減倍數有1/2和1/20兩種,通過單片機控制繼電器(TQ2-5),實現對兩種衰減倍數的切換;另外,電容網絡是進行相位補償,通過可調電容可以實現相位的補償。電壓跟隨電路作為隔離級,可減小后級電路對前級電路的影響。電壓跟隨電路由TI公司的OPA656構成,OPA656是寬帶單位增益穩定FET輸入運算放大器。

程控放大電路由程控增益芯片AD603和雙通道串口數/模轉換器TLV5638組成。單片機通過控制TLV5638的通道A產生高精度模擬電壓,用于調節AD603的放大倍數。直流偏置電路中,單片機控制TLV5638,使其OUTB引腳輸出一個直流電壓,該電壓經過NE5532組成的等比例反向器后接到OPA656的反向輸入端,可以通過這個電壓來確定OPA656的輸出,反映到屏幕上是波形的中線位置。如果液晶顯示的波形偏下或者偏上,可以調節TLV5638的B端輸出來調節。

評論