基于FPGA的數字示波器

2.4.2 FIFO及觸發電路設計

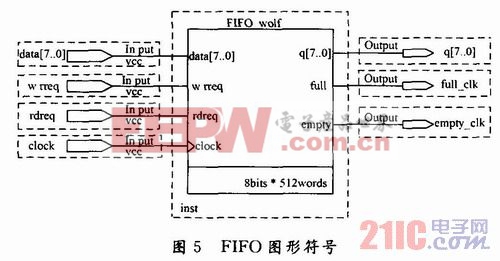

該系統利用FPGA設計大小為1 024 B的FIFO,實現對A/D采集數據的快速存儲。A/D采集電路開啟時,FIFO開始存儲數據。利用FPGA設計的FIFO如圖5所示。本文引用地址:http://www.j9360.com/article/191331.htm

當FIFO所存儲的數據在屏幕上還原出波形時,選取一個固定的起始點,使后面的波形能夠連續且沒有重疊的在屏幕上顯示。這個起始點反映到系統中就是觸發信號。該系統中采用內部軟件觸發方式,通過軟件設置觸發電平。所設置的施密特觸發器參數易于修改,從而抑制比較器產生的毛刺。當采樣值大于觸發電平,則產生一次觸發。該方式充分利用了FPGA的資源,減少外圍電路,消除硬件毛刺產生的干擾,易于調整觸發電壓。

2.4.3 SoPC系統設計

由于采集的數字信號需要進行高速處理,因此本設計利用了FPGA,高效的SoPC,對FIFO(數據緩存)中的數據進行處理,并控制TFT液晶顯示所采集信號的波形。

3 系統軟件設計

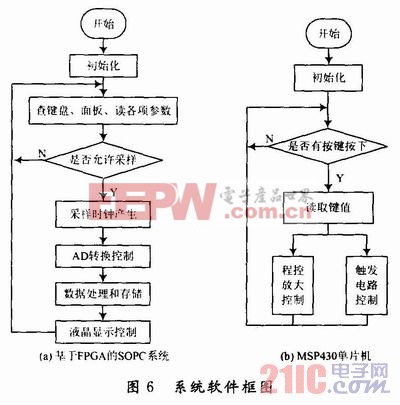

系統軟件設計實現了人機交互、信息提示、系統啟動與復位等功能。系統軟件設計如圖6所示,該系統包含采樣時鐘產生單元、顯存控制單元、TFT液晶顯示和可編程放大控制等模塊。Verilog可以形成原理圖,對其進行仿真實現,而且SoPC配置的軟核CPU允許掛接這些單元,很容易實現總體功能的合理規劃。

評論