優化FIR數字濾波器的FPGA實現

摘要:基于提高速度和減少面積的理念,對傳統的FIR數字濾波器進行改良。考慮到FPGA的實現特點,研究并設計了采用Radix-2的Booth算法乘法器以及結合了CSA加法器和樹型結構的快速加法器,并成功應用于FIR數字濾波器的設計中。濾波器的系數由Matlab設計產生。仿真和綜合結果表明,Booth算法乘法器和CSA算法加法器樹,在滿足FIR數字濾波器的性能要求的同時,在電路實現面積上、尤其是速度上有明顯的優化;并且當數據量越多時,優化也越明顯。

關鍵詞:Matlab;Booth算法;CSA算法;ISE

研究數字濾波器的意義就在于它們正日益成為一種主要的DSP(DigitaI Signal Processing)運算,并正在逐漸代替傳統的模擬濾波器。它可以保證任意幅頻特性的同時具有嚴格的線性相頻特性。而現場可編程門陣列(Field Programmable Gate Array,FPGA)可并行執行的特點決定它更加廣泛地應用于實時數字信號處理領域。不能想象今天的生活如果沒有音頻;視頻和言語交際的樣子,而這些都要應用數字信號處理技術。并且在任何時候,高性能,低規模,低成本都是設計的目標。濾波器(Finite Impulse Response,FIR)的實現方法有很多種,最常見的有串行結構和并行結構方法。前者根據FIR濾波器的實現表達式,將濾波器實質看作是做一個乘累加運算。一次乘累加運算的次數由濾波器的階數來決定。這種方法使用硬件資源相對較少,但速度較慢。并行結構的方法,將濾波器的串行實現展開,就可以直接用多個乘法器和加法器并行實現,其可以在一個時鐘周期內完成一次濾波,但要占用大量的乘累加器,器件延遲比較大。目前為了滿足面積和速度的需要,人們通常采用Booth算法、CSD算法,分布式算法等技術對FIR設計進行優化,優化效果各有利弊。本文針對串行結構對乘累加運算的乘和加分

別進行優化設計。分析了提高乘法器速度的途徑;針對多數據量的運算,提出了一種新型的快速加法器的解決方案。體現了優化設計中提高速度和減小面積的設計理念。同時給出并實現了一個16階FIR的設計實例。

1 用Matlab設計濾波器系數

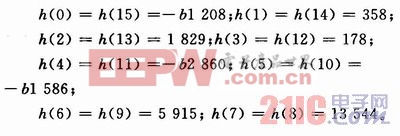

利用Matlab軟件的FDATool模塊,選擇濾波器類型為低通FIR,設計方法為窗口法,階數為16,窗口類型為Kaiser,數據采樣頻率fs為4.8 kHz,濾波器的截止頻率fc為1.08 kHz,導出的濾波器系數為16個15位的小數。將每一個系數擴大相同的倍數,最后四舍五人得到一系列整數系數。如下:

2 優化FIR濾波器在FPGA中的實現結構

2.1 FIR濾波器的基本算法原理

本文采用濾波器實現的基本的串行乘累加結構。FIR濾波器的差分方程可表示為:

![]()

式中:t為濾波器的階數。

其直接運算結構如圖1所示。

從公式(1)中可知FIR濾波器在硬件上的設計主要是完成乘累加功能,實現的一種方法是直接相乘累加。在實際應用中,當濾波器設計對濾波速度要求不高時,可采用串行結構或改進串行結構來實現,這樣可以選取資源較少的器件,降低設計成本;當對濾波速度有較高要求時,可以考慮采用并行或DA來實現。但要進行FIR運算,尤其在階數較高時,幾乎無法在FPGA內實現并行結構,所以這里采用串行運算的結構,僅使用一個乘加器。所以本文的設計著重于提高串行結構FIR的速度。下面將介紹一種高速的Booth算法乘法器和高速的加法器。

評論