基于FPGA無線傳感器網絡MAC控制器的設計

摘要 給出了一種由FPGA實現的無線傳感器網絡MAC控制器的設計方法,采用自頂向下的方法設計各個模塊,并在QuartusII8.0完成了仿真,該控制器主要支持IEEE802.15.4協議。測試結果表明,該MAC控制器支持20~250 kb·s-1數據傳輸速率,適應IEEE802.15.4協議要求。

關鍵詞 無線傳感器網絡;MAC;CSMA/CA

媒體訪問控制(Medium Access Control,MAC)協議處于無線傳感器網絡協議的物理層和網絡層之間。用于在傳感器節點間公平有效地共享通信媒介。它完成載波偵聽多路訪問(CSMA/CA)的信道存取、協議格式成幀或解幀、自動應答、系統多周期定時和幀校驗等功能。

不同傳感網絡的應用有著不同MAC協議,其中IEEE802.15. 4是最具代表性的協議。本文給出了用FPGA的控制邏輯來實現無線傳感器網絡MAC控制器的設計方法,并最終實現了符合IEEE802.15.4協議的控制器。

1 總體設計方案

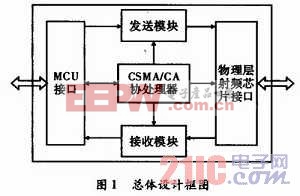

無線傳感器網絡控制器的FPGA設計包括無線傳感器網絡MAC子層的FPGA設計、MAC子層與上層協議的接口設計以及與物理層(PHY)的接口設計。該無線傳感器網絡的總體結構設計如圖1所示。整個系統分為發送模塊、接收模塊、CSMA/CA協處理器模塊、PHY接口模塊和MCU接口模塊5個部分。發送模塊和接收模塊主要完成MAC幀的發送和接收功能,包括MAC幀的封裝和解包,它直接提供了到外部物理層芯片(PHY)的串行接口。CSMA/CA協處理器是MAC的核心,控制接收和發送狀態機協調半雙工收發控制,并且通過程序執行的方式完成CSMA—CA算法。

2 模塊實現

2.1 MAC發送模塊

發送模塊可將上層協議提供的數據封裝之后通過PHY接口發送給PHY。發送狀態機按照幀的格式將數據進行封裝,分別在數據的前端添加前導序列和幀起始分隔符以及在數據的后端添加CRC校驗值,封裝后的整個數據包以串行格式發送出去。因此,發送部分的功能包括前導序列和幀起始分隔符插入、CRC計算、幀發送和自動應答等功能。

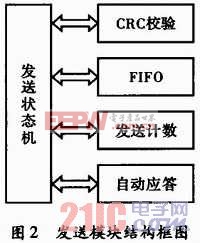

發送模塊包括發送FIFO(First In First Out)緩存器模塊(Tx_FIFO)、發送狀態機模塊(Tx_FSM)、自動應答模塊(Tx_Ack)、發送計數器模塊(Tx_Counter)和CRC計算模塊(Tx_Crc)等5個子模塊。其內部結構如圖2所示。

評論