基于FPGA實現千兆以太網業務在SDH上的傳輸

摘要:為了實現千兆以太網業務在SDH網絡上的傳輸(EOS),可以利用FPGA將以太網MAC數據幀在SDH數據幀中進行封裝和映射處理。介紹了GFP封裝協議以及虛級聯技術,給出了FPGA內部的模塊化設計方法。利用FPGA的強大功能和內部的豐富資源,簡化了電路設計的復雜性。千兆以太網在SDH中的傳輸增強了SDH設備的業務傳輸能力。

關鍵詞:以太網;SDH;GFP;EOS

0 引言

隨著人們對數據業務需求的不斷增長,以太網作為全世界應用最為廣泛的網絡通信技術之一,在全世界得到了大規模的普及。SDH是電信部門常用的通信傳輸設備,具有高可靠性和高安全性的特點。EOS(Ethernet over SDH)技術即借現有的SDH傳輸設備實現以太網業務的傳輸,具有非常重要的現實意義。

基于以太網的七層架構,在第二層數據鏈路層傳輸的是以太網的MAC幀。由于以太網和SDH系統的傳輸速率不匹配,需要通過封裝進行速率調整后才能映射到SDH的虛容器中。目前來講,常用的是GFP(Generic Framing Procedure)封裝。GE(千兆以太網)信號在SDH系統中的映射可以分為相鄰級聯和虛級聯兩種模式。相鄰級聯是在整個傳輸過程中保持連續帶寬,各個級聯的VC是相鄰的,在SDH網絡系統中需要有能夠進行相鄰級聯處理的中間設備,而虛級聯的應用方式比較靈活,將連續帶寬分解到多個VCs上傳輸,不一定相鄰,在傳輸的終端再將多個VCs重新組合成連續帶寬。因此,虛級聯方式有效地節省了帶寬,在系統中只需能夠進行處理的終端設備即可。在實際使用中,這種方式的應用比較廣泛。

1 FPGA收發模塊設計

本文實現的傳輸方式是在STM-16中傳輸1路GE信號,需要對以太網MAC幀進行GFP封裝。GFP幀分為GFP-F和GFP-T兩種模式,本設計采用的是GFP-F封裝模式。STM-16的傳輸速率是2.488 32 Gb/s。STM-16一共包括16路STM-1信號,STM-1的傳輸速率是155.52 Mb/s。STM-1信號采用虛級聯方式,利用VC-4-XV(X=1~7)最多采用7路STM-1信號即可傳輸1路GE信號。剩余STM-1通道的信號用來傳輸其他數據業務。

以太網數據在SDH設備中傳輸過程如下:在SDH發送部分中,以太網通過接口處理芯片產生MAC數據幀,通過GMII接口傳送給FPGA。FPGA將MAC幀進行GFP協議的封裝,然后映射到SDH的虛容器VC當中,再通過添加復用段和再生段開銷,生成STM-16數據幀,發送給光模塊再上到光網絡;在SDH接收部分中,光接收模塊從光網絡將STM-16數據幀接收F來發送給FPGA,FPGA在內部處理相關的開銷,再將GFP數據幀從VC虛容器中提取出來,通過解幀處理,將以太網的MAC幀還原出來,經過處理后發送給以太網。

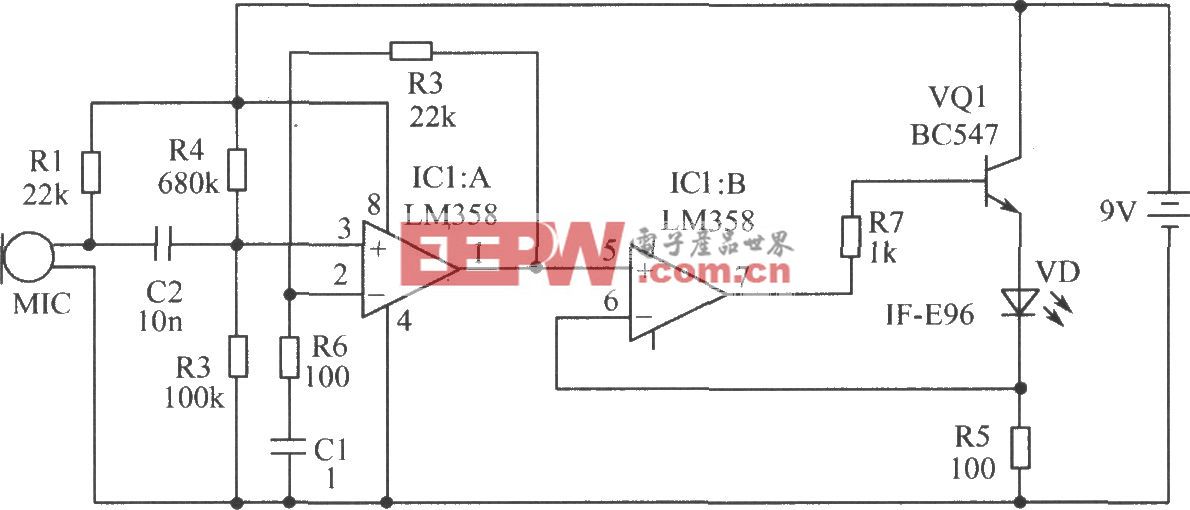

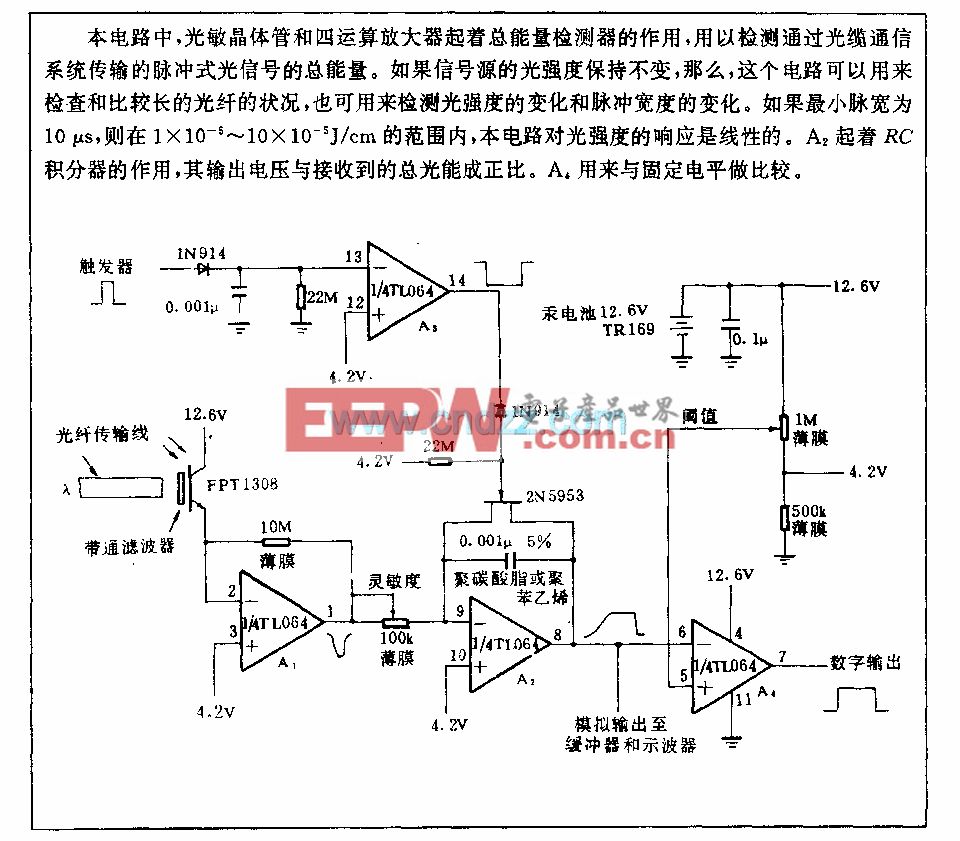

FPGA的內部設計可以分成發送模塊和接收模塊兩部分。其中,發送模塊可以分為以太網數據接收預處理模塊、GFP成幀模塊、SDH成幀模塊;接收模塊可以分為SDH解幀模塊、GFP解幀模塊、以太網數據發送處理模塊。發送和接收模塊示意圖分別如圖1和圖2所示。

發送部分的三個模塊的功能分別如下:以太網數據接收處理模塊利用FIFO緩存模塊存儲每一個有效MAC數據幀的數據和長度。同時實現數據從以太網時鐘域到SDH時鐘域的轉換;GFP成幀模塊對以太網MAC幀進行GFP封裝,通過調整GFP數據幀和GFP空閑幀的插入,將以太網MAC幀映射到SDH的高階VC-4虛容器中;SDH成幀模塊對虛容器進一步處理,添加開銷字段,生成STM-16數據幀,再利用FPGA內部的GTP接口將16位155. 52MHz的并行數據轉化為一路2 488.32 MHz高速LVDS差分信號發送出去。

接收部分實現的過程是發送部分的逆過程。

GFP成幀模塊分為GFP數據幀產生模塊、空閑幀產生模塊、插入幀選擇模塊、GFP擾碼模塊;GFP解幀模塊分為GFP幀同步模塊、GFP解擾模塊、GFP接收幀處理模塊。

GFP數據幀產生模塊在去掉MAC幀8 B前導碼后,將剩余部分的數據封裝為GFP數據幀。按照GFP協議添加4 B的核心頭部和4 B的凈負荷域頭部,將非定長的以太網MAC幀添加到凈負荷信息字段,在幀尾添加4 B的凈負荷幀校驗序列(FCS)。

空閑幀實際上屬于GFP用戶管理幀的一種,沒有凈負荷域,只包含一個GFP核心幀頭,是4 B的全0比特與序列“B6AB31E0”異或所得。

插入幀選擇模塊根據流量情況調整數據幀和空閑幀的插入,在沒有數據幀要發送時,插入空閑幀,以保證GFP數據流的連續性。

評論