基于FPGA實現千兆以太網業務在SDH上的傳輸

在整個FPGA設計中,接收端的幀同步模塊是比較重要的,它主要進行GFP幀的幀頭搜索和同步保持處理。同步狀態轉移圖如圖3所示。本文引用地址:http://www.j9360.com/article/190502.htm

用一個狀態機表示三種狀態,即搜索態、預同步態和同步態。在預同步狀態和同步狀態時都只取1幀進行狀態跳轉判斷。狀態機在FPGA初始化時默認處于搜索狀態,然后在連續的GFP數據流中進行幀頭的搜索判斷,將連續的數據流在每個時鐘周期按字節存入緩存器中,在每個時鐘周期進行4 B的擾碼判斷,即連續的4個字節與擾碼序列“B6AB31E0”進行異或,得到的4 B數據中前2個字節根據擾碼多項式G(x)=X16+X12 +X5+1生成2個字節的校驗值,然后與后2個字節進行比較,如果一致則表示找到了幀頭,進入到預同步態。在預同步態繼續在一幀幀頭的相應時刻進行幀頭的判斷,如果正確則跳轉到同步態,否則重新跳轉到搜索態,繼續尋找幀頭。如果進入到同步態,和預同步態一樣,也在一幀幀頭的相應時刻進行判斷,如果正確則繼續保持在同步態,否則跳轉到搜索態,重新在數據流中進行幀頭的搜索。只有在處于同步狀態時才能繼續對數據進行后續處理。

在SDH和GFP協議的成幀解幀里都要進行擾碼和解擾處理。SDH的擾碼多項式為G(x)=X7+X6+1,GFP對核心頭部PLI的擾碼多項式為G(x)=X16 +X12+X5+1,GFP凈負荷域的擾碼多項式為G(x)=x43+1。這些擾碼器都為串行擾碼器,對于GE這種速率的數據如果也采用串行處理方式的話,FPGA內部是無法實現的。經過轉換處理,可以將串行擾碼器變為并行擾碼器再進行擾碼,即可降低處理速度,滿足時序要求。

2 仿真綜合及實現

本設計采用VHDL硬件描述語言,使用的是XILINX公司帶有高速SERDES接口的SPARTAN-6芯片,利用ISE 12.1和仿真軟件進行了綜合和仿真。由于FPGA的內部資源較為豐富,本身自帶的IP核具有可靠性、方便性和靈活性的特點。時鐘部分使用了XIUNX芯片內部的DCM時鐘管理模塊,雙端口RAM以及FIFO緩存器都使用了FPGA的內部IP核資源。高速數據接口部分使用的是芯片內部的GTP模塊,去掉了外部高速接口轉換芯片,簡化了電路板的設計,不但提高了設計效率,也提高了系統設計的穩定性。

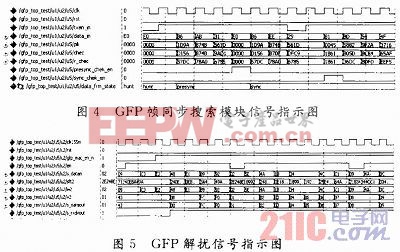

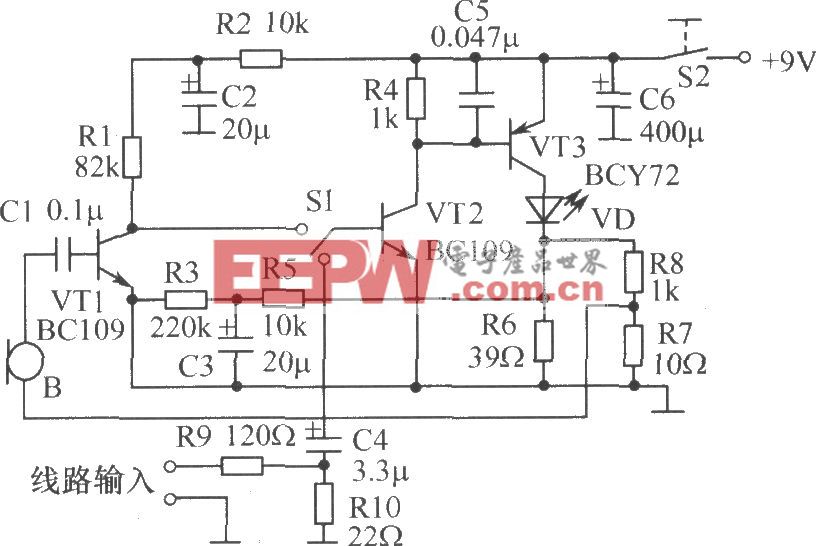

圖4和圖5表示的是對EOS數據進行VC-4-7V虛級聯后的部分時序仿真圖。

圖4中,data_frm_state信號表示的是幀同步狀態機。在數據流中,狀態機一開始處于hunt狀態,一旦找到幀頭,則進入到presync狀態;如果幀頭檢測沒有錯誤,則繼續跳轉到sync狀態;如果幀頭判斷正確,那么狀態機就一直保持在sync狀態。

圖5中,s_datain信號表示的是解碼前的數據,s_dataout信號表示的是根據擾碼多項式G(x)=X43+1解擾后的數據。

3 結語

綜上所述,利用FPGA可以實現千兆以太網MAC幀在SDH數據幀中的封裝和映射,配合外圍接口電路的使用,可以實現GE在STM-16中的傳輸。EOS技術既增強了以太網傳輸的覆蓋范圍,也豐富了SDH設備的傳輸接口,極大地方便了用戶的使用。同時,利用FPGA進行設計,大大縮短了開發的周期,也便于以后的升級和維護。

評論