基于FPGA高階FIR濾波器的實現

摘要:從FIR數字濾波器的基本結構模型出發,分析了FIR濾波器的設計思路及具體實現方法,詳細介紹了FIR濾波器的分布式算法(DA)結構。通過分析計算,得到普通DA結構實現高階濾波器會消耗大量的查找表資源,這樣的資源消耗甚至令硬件資源不可接受。針對普通DA的不足,提出了改進型DA結構。并利用FPGA仿真軟件分別時64階FIR帶通濾波器的兩種改進型DA結構進行仿真,結果表明改進型DA結構所消耗的資源大幅度降低。從而驗證了改進型DA結構在降低運算資源和提高性能等方面的優越性。

本文引用地址:http://www.j9360.com/article/190354.htm關鍵詞:FIR數字濾波器;分布式算法結構;改進型分布式算法結構;FPGA

在航天航空系統、雷達系統、遙感遙測系統等領域都涉及到如何在較強的背景噪聲和干擾信號下提取真正的信號,并隨著系統對寬帶、高速、實時信號處理要求越來越高,對濾波器的處理速度、帶寬等性能要求也隨之提高。數字濾波器的硬件實現方法主要有:DSP、專用芯片和FPGA。用DSP實現濾波器,其程序順序執行,因此運算速度隨濾波器階數的增加迅速下降;專用芯片實現的濾波器功能相對單一,靈活性小;而FPGA具有靈活的可編程邏輯和并行處理等優點,可很好地實現信號處理的實時性,同時,開發程序的可移植性好,可以縮短開發周期,因此FPGA實現數字濾波器的設計越來越受到重視和廣泛應用,本文數字濾波器的設計就是基于FPGA硬件實現。

1 FIR濾波器的基本模型

數字濾波器分為無限沖激響應濾波器(IIR)和有限沖激響應濾波器(FIR),IIR濾波器與FIR濾波器相比,IIR濾波器容易取得較好的通帶和阻帶特性,FIR濾波器系統穩定且容易實現線性相位。系統穩定和線性相位對系統的設計至關重要,故對FIR濾波器的普通分布式(DA)算法結構進行了分析探討與改進。FIR濾波器的網絡傳輸公式可由式(1)表示:

![]()

式中:x(k)為輸入函數;y(n)為輸出函數;h(n-k)為濾波器系數;N為濾波器的階數。根據式(1),FIR濾波器的結構如圖1所示。

2 FIR濾波器的設計及實現

2.1 FIR濾波器設計

FIR濾波器的設計方法有:窗函數法、頻率抽樣法和最佳一致逼近法。本文以窗函數法為例介紹一下濾波器設計。設窗函數為凱賽窗,通帶截至頻率fc、阻帶起始頻率fa、通帶紋波δp和阻帶紋波δa,則濾波器階數N的計算如式(2)所示:

![]()

式中fs為抽樣頻率。由式(2)可見,通帶和阻帶的紋波系數越小,濾波器的階數越高。因此在設計FIR濾波器時,需要在階數,紋波系數和過渡帶之間進行權衡,選出合適的模型。

2.2 FIR濾波器具體買現

相比用DSP實現FIR數字濾波器,采用FPGA實現可以獲得更快的速度,同時還可采取各種算法降低運算資源,提高性能,分布式算法(DA)就是其中一種。隨著大規模集成電路的發展,特別是可編程邏輯器件的發展,DA算法在數字濾波器硬件設計中的研究進一步加強。

2.2.1 DA算法結構

DA算法結構是將乘法運算轉換成基于查找表的加法運算,其基本原理為通過比特串行運算產生兩組內積結果代替乘法器結構,如式(3)所示:

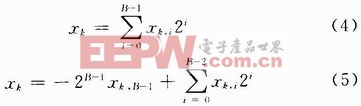

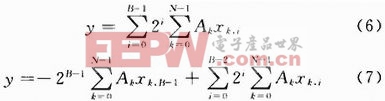

式中:Ak為濾波器系數;xk為濾波器輸入;N為濾波器階數;y為濾波器輸出。對于無符號數和有符號數xk的二進制表示式分別為式(4)和式(5):

式中:xk,i為xk的每位二進制數,值為0或1;B為xk的二進制位數。將式(4)和式(5)分別帶入式(3)中,可得式(6)和式(7):

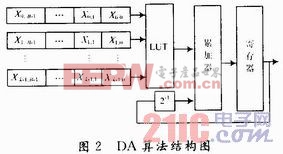

在濾波器設計中,一般采用有符號數,由式(6)和式(7)可知,有符號數的計算公式含有了無符號數的計算,因此本文以有符號數為例來介紹DA算法的具體實現。DA算法結構的實現過程如圖2所示。

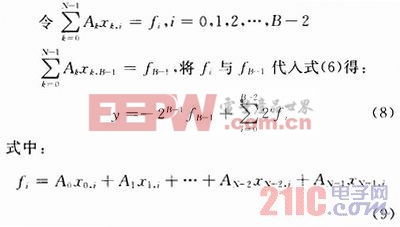

對于FIR濾波器來說,A0至AN-1為常數,因此由式(8),式(9)和式(10)可看出,y的值僅與系數的各種組合有關,這種結構可以利用查找表來實現。設FIR濾波器階數為N,系數的量化位數為M為,則需要存儲器(ROM)深度和寬度的計算公式分別為式(11)和式(12)所示:

![]()

![]()

評論