基于FPGA的出租車計價系統設計

摘要:設計出租車計價系統,運用自頂向下的設計思想,以芯片CycloneⅡEP2C8T144C8為設計核心,采用QuartusⅡ仿真軟件,對設計電路的各模塊及整個系統進行了EDA仿真驗證。結果表明,該計價系統具有計時、計費、計程和動態顯示的功能,符合設計要求,修改VHDL語言源程序,可完成更多的出租車計價系統的擴展功能。

關鍵詞:出租車計價;自頂向下;VHDL;FPGA

0 引言

隨著電子技術的發展,出租車計價器的設計也從傳統的全部由機械元器件組成的機械式設計到半電子式(即用電子線路代替部分機械器件的出租車計價器),再從集成電路式到目前基于FGPA芯片為核心的系統的設計共經歷了四個階段,利用FPGA芯片,用較少的外部硬件和適當的軟件相互配合,可以通過軟件編程來完成更多的附加功能,設計比較靈活,并且還具有功耗小,體積小、低成本、安全可靠、使用方便等優點。因此,使用FPGA來設計出租車計價系統已受到人們的關注,也能更好地發揮其優點。

本文以FPGA為設計載體,通過VHDL語言編程,采用QuartusⅡ仿真軟件,設計了一種能動態顯示出租車計時、計費、計程的系統,具有一定的實際應用價值。

1 出租車計價系統的設計要求

1.1 實現計費功能

車起步開始計費,首先顯示起步價(本次設計為8.0元),行程在3 km以內,按起步價收費;當行駛超過3 km,1.6元/km,車暫時停車(如遇紅綠燈或中途暫時停車),當等待時間超過3 min,按1元/min收費。

1.2 實現顯示功能

能動態顯示出租車行駛的里程,范圍為00~99 km(考慮到出租車就在市區或近郊附近活動),同時顯示等待時間,范圍為00~59 min,顯示總計價值,范圍為00~999.9元,計價分辨率為0.1元。

2 出租車計價系統的設計體系

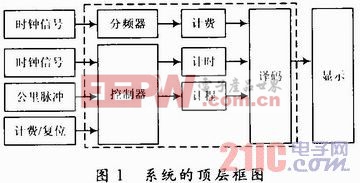

圖1為整個系統的頂層框圖,根據層次化設計理論,將出租車自動計價系統自頂向下可分為分頻模塊、控制模塊、計量模塊、譯碼和動態掃描顯示模塊。

(1)分頻模塊。通過分頻產生不同頻率的脈沖信號用來實現系統的計費,本次設計中通過對240 Hz的輸入脈沖進行15次,24次和240次分頻,得到16 Hz,10 Hz和1 Hz的三種頻率,分別用于1.6元,1元和0.1元的計費。

(2)計量控制模塊。計量控制模塊是出租車自動計費器系統的主體部分,該模塊主要完成出租車的計時、計價、計程功能。計時器的量程為59 min,滿量程自動歸零。計程器的量程為99 km,滿量程自動歸零。行程在3 km內,且等待累計時間在3 min內,起步價費為8元;3 km外以1.6元/km計費,等待累計時間超過3 min按1元/min計費。

(3)譯碼顯示模塊。該模塊經過8選1數據選擇器將計費數據(4位BCD碼)、計時數據(2位BCD碼)、計程數據(2位BCD碼)動態顯示輸出。其中計費數據最大顯示為999.9元;計時數據最大顯示為59 min;計程數據最大顯示為99 km。

評論